一種應用于UHF讀寫器的數字跳頻技術

摘要:針對超高頻(UHF)讀卡器在實際應用中容易出現盲區而無法順利讀取標簽的情況,提出了應用于UHF讀寫器的數字跳頻技術方案。通過上位機軟件發送數字跳頻參數給FPGA,FPGA根據得到的參數對集成鎖相環芯片Si4133、功率放大器RF2173及外設進行配置,得到數字跳頻的栽波信號。測試結果證明,該方案應用于UHF讀卡器項目中,能順利讀到標簽。

關鍵詞:UHF讀寫器;RFID;數字跳頻;頻率合成

引言

RFID技術的發展為物聯網的廣泛應用提供了技術支持,超高頻(UHF)讀寫器憑借讀取距離遠、速度快的特點,未來必將在各個行業得到廣泛的應用。目前,國內的大部分UHF讀寫器都是基于單頻點或者頻帶較窄,在讀取標簽的過程中容易出現盲區,導致無法順利讀取標簽。

本文提出了一種基于FPGA的數字跳頻技術,通過上位機設置中心頻點和跳頻步進,利用FPGA對集成鎖相環芯片進行配置,得到期望的頻率,實現跳頻讀取標簽,從而解決了實際情況中的盲區問題。

1 總體框架

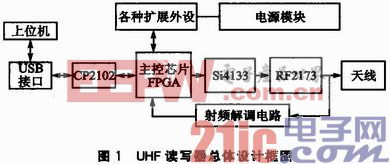

UHF讀寫器總體設計框圖如圖1所示。主控芯片采用Altera公司的Cyclone III系列FPGA芯片EP3C25Q240C8。該芯片有24 624個LE、149個用戶I/O口、608 256位存儲器、4個鎖相環;外部接口多,資源豐富,非常適合在早期研發階段擴展各種功能。

FPGA外擴512MB SRAM和64 MB NOR Flash存儲器,能夠實現SOPC設計、操作系統移植、讀寫器擴展的功能(比如網絡接入能力);有USB外設,方便數據的USB傳輸;利用串口轉USB芯片CP2102,可方便上位機軟件實現對硬件的配置參數進行控制。

FPGA從上位機發送的命令碼中解碼出各種配置參數,完成射頻發射電路中Si4133中心頻率以及跳頻步進的設置,對功率放大器芯片RF21 73的工作模式進行選擇,實現EPC GEN2協議規定的與標簽交互命令的PIE編碼和FM0,Miller 2、4、8解碼,將讀取到的標簽EPC通過串口發送給上位機軟件,實現人機交互。

2 鎖相環芯片Si4133工作原理

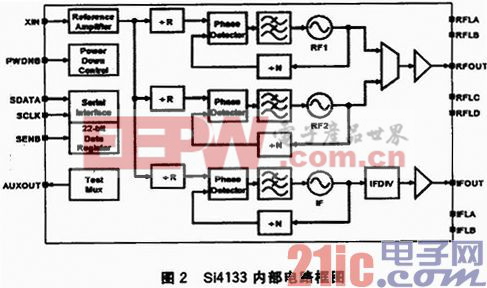

Si4133是Silicon Laboratories公司推出的一款應用于GSM和GPRS無線通信的芯片,內部含有集成壓控振蕩器的多邊帶射頻頻率合成器。其內部框圖如圖2所示。

pa相關文章:pa是什么

鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論