帶有時(shí)標(biāo)的嵌入式語音信號(hào)錄取系統(tǒng)設(shè)計(jì)

Audio控制器由有限狀態(tài)機(jī)(FSM)、數(shù)據(jù)緩存器(FIFO)和總線接口三部分組成,如圖2所示。FSM完成WM8731數(shù)據(jù)讀寫的控制、FIFO讀寫與存儲(chǔ)狀態(tài)控制以及總線接口控制。FIFO用來緩沖WM8731采集得到的數(shù)據(jù),防止數(shù)據(jù)丟失,并使系統(tǒng)工作在異步模式,大大提高了CPU的工作效率。總線接口作為橋梁,用以連接NiosⅡ和FIFO。本文引用地址:http://www.104case.com/article/148063.htm

2.3 數(shù)據(jù)存儲(chǔ)系統(tǒng)的設(shè)計(jì)

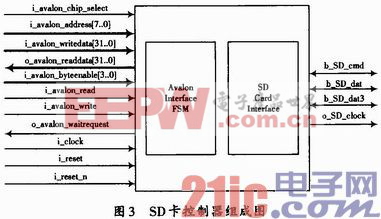

為了實(shí)現(xiàn)大容量數(shù)據(jù)存儲(chǔ),本采集系統(tǒng)選用當(dāng)下比較流行SD卡作為存儲(chǔ)介質(zhì)。由于SD卡采用的是串行讀寫方式,時(shí)序較為復(fù)雜,且其數(shù)據(jù)量較大,故采用Verilog編寫了SD控制器,其結(jié)構(gòu)如圖3所示。Avalon Interface FSM與Avalon總線相連接,用來完成控制器與NiosⅡ處理器通信;SD Card Interface與SD卡相連,完成數(shù)據(jù)的串/并轉(zhuǎn)換和時(shí)序控制。

3 軟件程序設(shè)計(jì)

本采集系統(tǒng)軟件在Nios EDS環(huán)境下進(jìn)行開發(fā),由于程序中只有一個(gè)線程,結(jié)構(gòu)比較簡單,故并未采用操作系統(tǒng)。主程序在完成各個(gè)模塊初始化后進(jìn)入等待狀態(tài),GPS的串口數(shù)據(jù)、PPS觸發(fā)信號(hào)和按鍵觸發(fā)信號(hào)采用中斷形式,利用中斷服務(wù)子函數(shù)完成各項(xiàng)功能。

3.1 時(shí)間信息的解析

由于GPS接收機(jī)M12MT具有多種數(shù)據(jù)輸出格式,其中時(shí)間格式默認(rèn)為為格林威治標(biāo)準(zhǔn)時(shí)間,故為了保證數(shù)據(jù)解析的正確性,在系統(tǒng)啟動(dòng)后首先對GPS接收機(jī)進(jìn)行初始化,使其時(shí)區(qū)設(shè)定為GMT+8,每秒鐘串口輸出一組數(shù)據(jù),格式采用@@Eq形式。

由于UART控制器每收到1個(gè)字節(jié)即產(chǎn)生一個(gè)中斷,故NiosⅡ處理器首先需要對接收到的數(shù)據(jù)進(jìn)行緩存,當(dāng)收到5個(gè)字節(jié)后判斷是否是報(bào)頭,如果是報(bào)頭就繼續(xù)接收,否則計(jì)數(shù)器清零并重新進(jìn)行緩沖。在報(bào)頭解析正確后,處理器將所有報(bào)文依次接收并存儲(chǔ)到緩沖區(qū)中,緩沖區(qū)中的前18位即是時(shí)間數(shù)據(jù),其格式為mm,dd,yy,hh,mm,ss。

需要特別說明的有兩點(diǎn):第一,由于每一秒的PPS信號(hào)早于串口數(shù)據(jù)的輸出,故處理器需要對接收到的時(shí)間加1 s,而后利用下一個(gè)PPS信號(hào)進(jìn)行觸發(fā);第二,GPS接收機(jī)在鎖定3顆以上衛(wèi)星時(shí)時(shí)間數(shù)據(jù)才具有可靠性,故需要判斷報(bào)文中的fix標(biāo)志位,如果fix位是1,這表明衛(wèi)星已鎖定,時(shí)間信息可靠,PPS信號(hào)可以作為觸發(fā)信號(hào)。

3.2 采集數(shù)據(jù)的封裝

Audio控制器輸出的數(shù)據(jù)是按照采樣時(shí)刻先后順序生成的一系列二進(jìn)制數(shù)值點(diǎn),為了加入起始時(shí)刻的時(shí)間標(biāo)志,同時(shí)便于評(píng)估系統(tǒng)進(jìn)行后續(xù)處理,本錄取系統(tǒng)對采樣起始時(shí)刻和采樣數(shù)據(jù)進(jìn)行封裝。首先將采樣數(shù)據(jù)封裝成WAV文件格式,加入相應(yīng)的格式標(biāo)志、采樣率、采樣精度、聲道數(shù)、數(shù)據(jù)長度等信息,然后再在WAV文件的前面加入二進(jìn)制的時(shí)間信息形成DAT格式文件。評(píng)估系統(tǒng)通過DAT文件中的時(shí)間信息和WAV文件中的采樣率等信息即可計(jì)算出每個(gè)采樣點(diǎn)的絕對時(shí)間。

3.3 文件系統(tǒng)的引用

為了提高SD卡存儲(chǔ)的兼容性,便于通用計(jì)算機(jī)對SD卡的寫入和讀取,本錄取系統(tǒng)利用FAT文件系統(tǒng)對SD卡進(jìn)行讀寫操作。由于處理器中沒有使用操作系統(tǒng),故需要自己移植文件系統(tǒng)和編寫底層驅(qū)動(dòng)函數(shù)。

本錄取系統(tǒng)中的文件系統(tǒng)采用層次結(jié)構(gòu)設(shè)計(jì),共分為3層,即硬件描述層(HAL)、功能層和應(yīng)用層。硬件描述層完成SD卡檢測、控制命令的寫入、數(shù)據(jù)的讀寫等功能;功能層完成塊數(shù)據(jù)的讀寫、查找、替換等功能;應(yīng)用層完成格式化、文件建立與刪除、文件寫入與讀出等功能。主函數(shù)調(diào)用應(yīng)用層的功能函數(shù)即可完成對SD卡的文件操作。

4 結(jié)論

本文介紹了一種利用SOPC技術(shù)在FPGA平臺(tái)上實(shí)現(xiàn)帶有時(shí)標(biāo)的嵌入式語言信號(hào)錄取系統(tǒng),不但論述了錄取系統(tǒng)的結(jié)構(gòu)組成與工作原理,而且對GPS控制器、Audio控制器、SD卡控制器等硬件設(shè)計(jì)和GPS時(shí)間解析、采集數(shù)據(jù)的封裝、文件系統(tǒng)的引用等軟件編寫進(jìn)行了詳細(xì)的介紹。經(jīng)實(shí)際使用驗(yàn)證,本錄取系統(tǒng)能夠在GPS時(shí)間觸發(fā)下完成語音信號(hào)的錄取,錄取得到的數(shù)據(jù)帶有時(shí)標(biāo)信息,能夠滿足語音電臺(tái)抗干擾客觀評(píng)估系統(tǒng)的技術(shù)要求。

評(píng)論