DDR測試技術和工具是否跟上了時代步伐?

DDR是雙倍數據速率的SDRAM內存,如今大多數計算機系統、服務器產品的主流存儲器技術,并且不斷向嵌入式系統應用領域滲透。孰不知,隨著iPhone等大牌智能手機的采納,DDR內存儼然成為智能手機轉變的方向之一,例如韓國泛泰去年底最新推出的Android智能手機Vega X就搭載了512MB的DDR2內存。

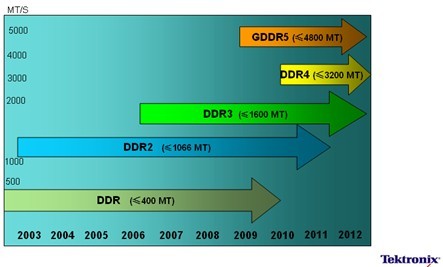

本文引用地址:http://www.104case.com/article/118356.htmDDR技術不斷發展,并行總線達到了串行技術的速度,時鐘速度達到1GHz。目前,DDR3現在已經具備1.6Gb/s的數據速率,而DDR3-1866及更高速率版本正在開發中,很快就會出現在市場上。目前主流的DDR2也有多種速度、多種容量和多種規格,從DDR-266的266MT/S、133MHz、2.5V電壓,已經發展到了現在的DDR2-1066的1066MT/S、533MHz、1.8V電壓。另外,低能耗DDR(LP-DDR,用于便攜式計算機)和顯存GDDR也是DDR的發展變化版本。目前主流的DDR也有多種速度、多種容量和多種規格,從DDR-266的266MT/S、133MHz、2.5V電壓,已經發展到了現在的DDR3-1600,1.5V電壓。另外,低能耗DDR(LP-DDR,用于便攜式計算機)也是DDR的發展趨勢之一。

圖1:DDR存儲器的設計正超過千兆位數據速率,時鐘速度就要達到1GHz,帶來了更大的測試挑戰。

技術的升級和應用領域的拓展,都使DDR存儲器的驗證和測試更具挑戰性。高數據速率和時鐘速度使得時序余量更緊張,導致串擾、阻抗匹配和抖動問題加劇,這需要使用高速測試測量技術和性能更高的測試測量工具,以獲得更好的信號捕獲能力、測試精度等。

DDR測試要點和難點

鑒于DDR的stub(短線)拓撲結構和緊張的時序容限,在驗證和測試中要求檢驗多種指標,包括:電氣電源和信號電源質量,噪聲、毛刺和地彈/地跳;時鐘信號質量,上升時間和下降時間/slew rate ;命令、地址和數據有效窗口(建立/保持時間);DQS/DQ/時鐘偏斜。

DDR數據速率的不斷提升使得存儲系統的信號完整性問題日益凸顯。因此必須將物理層的信號與系統級的時序關聯起來,避免時序沖突、協議背離、時鐘抖動以及由總線引發的錯誤,確保存儲系統準確工作。需要關聯的時序包括:存儲器初始化時序;SDRAM模式寄存器操作(MSR);讀/寫數據有效窗口;休眠狀態的時序;普通工作狀態的時序。

至于DDR測試的難點,泰克的技術支持工程師余嵐最近在IIC-China的一場研討會中指出:“第一,DDR數據信號DQ和DQS是雙向的,所以讀信號和寫信號會同時出現在數據線上,比較難分離那些數據是讀數據哪些數據是寫數據;第二,就是探測問題,DDR2或者3使用的是BGA封裝,測試管腳隱藏在芯片的底下,因此探頭的選擇非常重要。另外由于DDR2和DDR3速率非常高,所以對于帶寬和探測信號保真度要求就格外的高,而且很多時候我們光靠示波器已經滿足不了測試的要求了,需要聯合比如邏輯分析儀等進行協議和時序的聯合測試。”

余嵐表示,帶寬/上升時間、采樣率、觸發方式、內存軟件、探頭是DDR測試選擇示波器的重要考量指標,其中帶寬/上升時間是重中之重,包括連接、信號保真度。但需要聯合邏輯分析儀等設備時,通道數和采樣率是最重要的考慮因素。

存儲器相關文章:存儲器原理

評論