使用EYEQ特性實現高速串行IO的最佳相位接收判決

—— Using EYEQ Characteristics to Realing Best Phase Receiver Sentence of High-Speed Serial IO

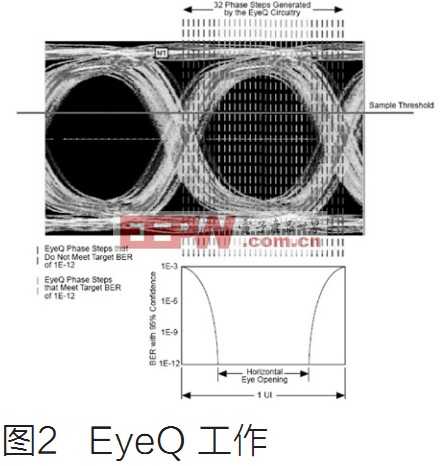

現有的很多高速串口協議,都要求很低的誤碼率,比如CEI-6G-LR(6.375G, 40英寸走線)就要求1E-15的誤碼率。為滿足此類低誤碼率要求,ALTERA高端的FPGA STRATIX IV系列,提供了片上信號質量檢測電路(EYEQ),幫助客戶在高速串行IO接收處找到最優的采樣位置。

本文引用地址:http://www.104case.com/article/116959.htm通常眼圖的張開度是用來衡量接收端信號的質量。片上信號質量檢測電路(EYEQ)就是一個調試診斷工具來幫助分析接收的數據路徑,包括接收端的增益,噪聲水平。

原理

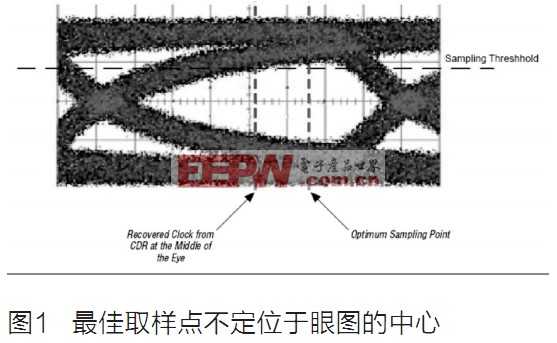

缺省情況下,CDR恢復時鐘是在眼圖的中間位置采數據,如圖1的紅色虛線位置,但是根據這個眼圖的張開程度,最佳采樣位置應該是在綠色虛線部分。只有在綠色虛線位置,眼高最大,這樣采樣到的數據才具有最低的誤碼率。

EYEQ電路在一個完整的信號周期(UI)中,將采樣時鐘放到32個相位上,用戶可以根據每個不同相位時的誤碼率,找出最佳采樣相位。如圖2所示。

評論