借助智能DAQ, 獲得高級數據采集技術

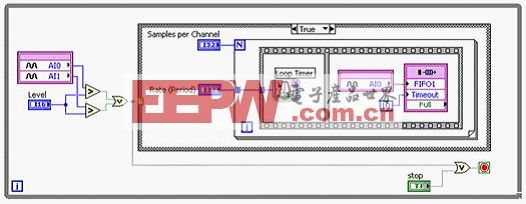

上圖既沒有針對全局通道、采樣時鐘、觸發的配置函數,也沒有開始、停止和清除等任務。 所有內容都被1個簡單的模擬I/O讀取所取代;全部定時都為本地LabVIEW結構(如:While循環和條件結構)所控制。由于整個程序框圖均在 FPGA硬件內執行,LabVIEW代碼的運行便體現出硬件定時的速度和可靠性。

本文引用地址:http://www.104case.com/article/107898.htm讓我們更深入地了解一下該程序框圖的運行方式。 模擬I/O節點并不指定某個采樣速率,而使用For循環采集各個樣本。 與之對應的ADC在I/O節點被調用時,負責對輸入信號進行實際數字化,因而通過For循環接受定時。 若想在100 kHz的頻率下進行信號采樣,針對循環的延遲就必須設定為10 µs。 循環的定時器函數從第2輪循環迭代開始便確保著特定的時間延遲,用戶因而能夠通過順序結構保證樣本之間存在著指定的時間間隔。 NI LabVIEW FPGA中功能強大的條件結構,實際代表了用于封裝各類代碼的硬件觸發。 由于所有的函數和結構都通過邏輯單元在硬件內運行,所以條件結構確保開始具有實時10 µs時間精度的采樣。 最后需指出的是,由于操作位于硬件層,只涉及幾個層次的抽象處理,因此用戶無需清除任務ID或釋放內存。

就基于FPGA的智能DAQ硬件而言,其真正的優勢是能夠定制各類定時和觸發,并在硬件中進行信號處理和決策。 現在讓我們了解一下:針對某類自定義應用,需對模擬輸入觸發做出哪些修改。 若我們希望在2路模擬輸入通道的某路電壓超過指定范圍時便觸發采集,又該如何修改呢? 借助NI LabVIEW FPGA,此類任務的執行易如反掌。

圖 3. 通過智能DAQ和NI LabVIEW FPGA實現的自定義觸發式模擬輸入

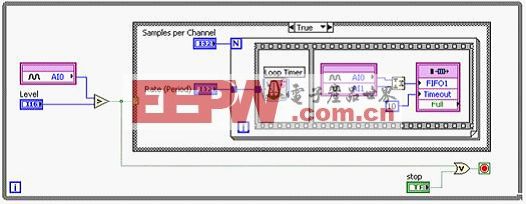

這里,我們已經為程序框圖添加了第2個I/O節點和第2個比較函數,以及1個布爾“或”函數。 智能DAQ硬件為所有的模擬輸入通道提供專用ADC,因而2路通道能夠接受同步采樣;同時,只要任何1路通道的電壓超過了指定范圍,條件結構便會執行 “真”條件,并開始以10 µs時間精度進行采樣。 請記住:缺少智能DAQ便不可能生成類似的觸發;在其他DAQ硬件上應用時,觸發需要具有更高延遲的軟件定時來實現。 如果此后我們希望通過擴展將監控范圍從2路通道延伸至全部8路通道,甚至希望添加數字觸發,就需要簡化自定義代碼。 添加預觸發掃描后,用戶便可對輸入通道不斷進行采樣并將數據傳送至FIFO緩沖器。 觸發器一旦接受讀取,FIFO緩沖器和此后的采樣便可經由DMA通道,被傳送至主機。

如果我們希望借助NI-DAQmx驅動,對第2模擬輸入通道進行采樣,則該程序框圖與圖1所示的內容相差無幾。然而限制依然存在,因為2路通道均被迫引用 相同的觸發器并以相同的時鐘頻率進行采樣。 現在我們來看看:智能DAQ和NI LabVIEW FPGA幫助實現的各類多通道采樣。

圖4. 通過智能DAQ實現的觸發式同步模擬輸入

圖4(上圖)展現了:如何基于模擬輸入通道0中的模擬觸發器,對2路不同的模擬輸入通道進行同步采樣。由于智能DAQ設備均配有獨立的ADC,在同一 I/O節點中的2路通道可在完全相同的時刻接受采樣。 典型的多功能DAQ設備可通過一個ADC多路復用所有通道,因此,各路通道必須共享相同的采樣時鐘和觸發線。 圖5(下圖)展現了:智能DAQ硬件其實能夠以獨立的速率,對不同的模擬輸入通道進行采樣。 在獨立回路中放置模擬輸入I/O節點后,每路通道會以完全不同的速率進行采樣,然后各自通過2條DMA通道讀寫硬盤。

評論