fsp:fpga-pcb 文章 最新資訊

駿龍科技最新物聯(lián)網(wǎng)開發(fā)套件和電機(jī)驅(qū)動方案擴(kuò)展Altera MAX 10 FPGA的應(yīng)用

- 領(lǐng)先的技術(shù)分銷商駿龍科技有限公司發(fā)布了基于Altera MAX® 10的“Mpression Odyssey(奧德賽)”物聯(lián)網(wǎng)開發(fā)套件和電機(jī)驅(qū)動方案。Altera的MAX® 10 FPGA在低成本、單芯片、瞬時上電的可編程邏輯器件中提供了先進(jìn)的處理能力,駿龍科技推出的產(chǎn)品進(jìn)一步驗(yàn)證了MAX® 10 FPGA的卓越性能,并進(jìn)一步豐富了Altera公司的工業(yè)解決方案。 “Mpression Odyssey(奧德賽)”開發(fā)套件是一

- 關(guān)鍵字: 駿龍科技 物聯(lián)網(wǎng) FPGA

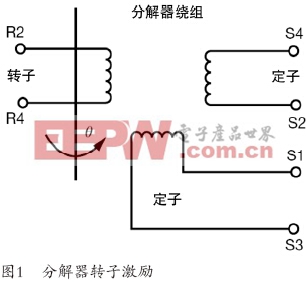

利用FPGA和分解器數(shù)字轉(zhuǎn)換器簡化角度測量

- 1 編碼器和分解器的類型 編碼器分為增量和絕對兩個基本類別。增量編碼器可以監(jiān)控輪軸上的兩個位置,可以在輪軸每次經(jīng)過這兩個位置時產(chǎn)生A或B脈沖。獨(dú)立的外部電動計數(shù)器然后從這些脈沖解讀出轉(zhuǎn)速和旋轉(zhuǎn)方向。雖然適用于眾多應(yīng)用,但是增量式計數(shù)器確實(shí)存在某些不足。例如,在輪軸停轉(zhuǎn)情況下,增量編碼器在開始運(yùn)行之前必須首先通過調(diào)回到某個指定校準(zhǔn)點(diǎn)來實(shí)現(xiàn)自身校準(zhǔn)。另外,增量式計數(shù)器易受到電氣干擾的影響,導(dǎo)致發(fā)送到系統(tǒng)的脈沖不準(zhǔn)確,進(jìn)而造成旋轉(zhuǎn)計數(shù)錯誤。不僅如此,許多增量編碼器屬于光電器件,如果對目標(biāo)應(yīng)用有影響,則

- 關(guān)鍵字: 編碼器 分解器 RDC FPGA 脈沖

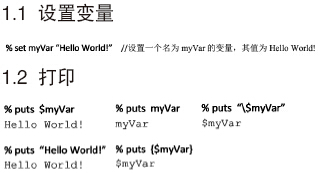

Tcl在Vivado中的應(yīng)用

- Xilinx的新一代設(shè)計套件 Vivado 相比上一代產(chǎn)品 ISE, 在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。 但是對初學(xué)者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為了快速掌握 Vivado 使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到 Vivado 的信心。 本文介紹了 Tcl 在 Vivado 中的基礎(chǔ)應(yīng)用,希望起到拋磚引玉的作用,指引使用者在短時間內(nèi)快速掌握相關(guān)技巧,更好地發(fā)揮 Vivado 在 FPGA 設(shè)計中的優(yōu)勢。 1

- 關(guān)鍵字: Xilinx VivadoTcl FPGA cells

Mentor Graphics為電子工程師提供性價比超值的高級電路設(shè)計解決方案,重新定義PCB市場格局

- 明導(dǎo)(Mentor Graphics Corporation)今天宣布以史無前例的5000美元起始價推出三款全新PADS®系列產(chǎn)品,以滿足電子工程師日益提高的設(shè)計需要。除了具備以前領(lǐng)先市場的PADS產(chǎn)品的易學(xué)易用等特點(diǎn)之外,全新的PADS系列還融合了高效設(shè)計與分析技術(shù),性價比極高,可以處理各種復(fù)雜的電子問題。該系列產(chǎn)品是在以前積累的強(qiáng)大的PADS技術(shù)經(jīng)驗(yàn)基礎(chǔ)上延伸而來的,這些經(jīng)驗(yàn)經(jīng)過了全球數(shù)以百萬計工程師的數(shù)百萬次設(shè)計的實(shí)踐檢驗(yàn),在某些情況下還利用了領(lǐng)先市場的Xpedition®套件中

- 關(guān)鍵字: Mentor PCB

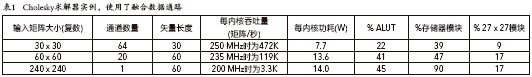

Altera: FPGA集成硬核浮點(diǎn)DSP

- 1 FPGA浮點(diǎn)運(yùn)算推陳出新 以往FPGA在進(jìn)行浮點(diǎn)運(yùn)算時,為符合IEEE 754標(biāo)準(zhǔn),每次運(yùn)算都需要去歸一化和歸一化步驟,導(dǎo)致了極大的性能瓶頸。因?yàn)檫@些歸一化和去歸一化步驟一般通過FPGA中的大規(guī)模桶形移位寄存器實(shí)現(xiàn),需要大量的邏輯和布線資源。通常一個單精度浮點(diǎn)加法器需要500個查找表(LUT),單精度浮點(diǎn)要占用30%的LUT,指數(shù)和自然對數(shù)等更復(fù)雜的數(shù)學(xué)函數(shù)需要大約1000個LUT。因此隨著DSP算法越來越復(fù)雜,F(xiàn)PGA性能會明顯劣化,對占用80%~90%邏輯資源的FPGA會造成嚴(yán)重的布線擁

- 關(guān)鍵字: Altera FPGA LUT DSP 數(shù)據(jù)通路

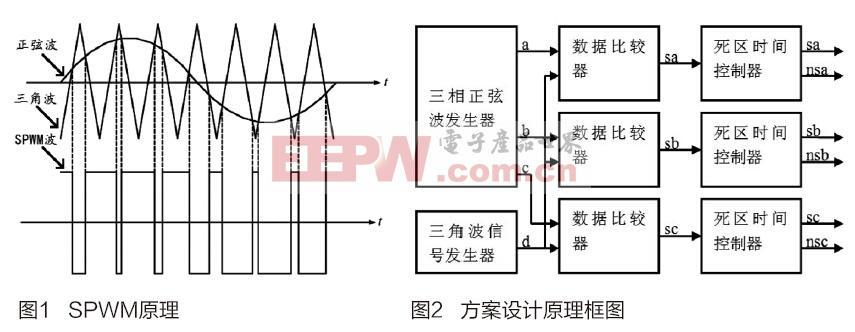

三相SPWM波形發(fā)生器的設(shè)計與仿真

- 本文提出了一種采用VHDL硬件描述語言設(shè)計新型三相正弦脈寬調(diào)制(SPWM)波形發(fā)生器的方法。該方法以直接數(shù)字頻率合成技術(shù)(DDS)為核心產(chǎn)生三相SPWM信號。并且利用VHDL設(shè)計了死區(qū)時間可調(diào)的死區(qū)時間控制器,解決了傳統(tǒng)的模塊電路等待方法很難產(chǎn)生帶精確死區(qū)時間控制的SPWM信號的問題。該方法在Quartus II 9.1環(huán)境平臺下進(jìn)行了仿真驗(yàn)證,并將設(shè)計程序下載到DE2-70實(shí)驗(yàn)板進(jìn)行實(shí)驗(yàn)測試,用示波器測試得到了死區(qū)時間可控制的SPWM波形。

- 關(guān)鍵字: VHDL SPWM DDS 死區(qū)時間 FPGA 201505

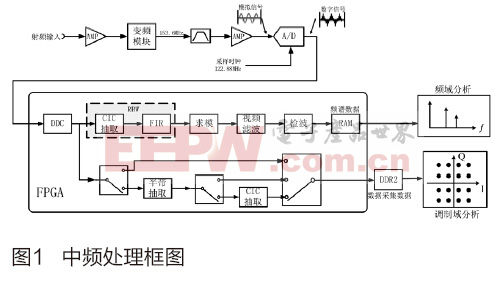

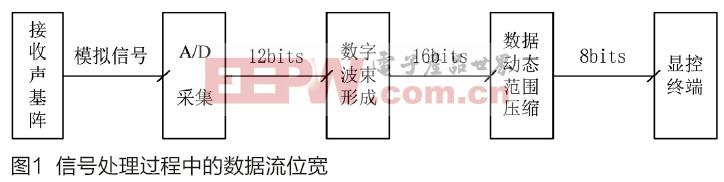

聲納圖像動態(tài)范圍擴(kuò)展與FPGA實(shí)現(xiàn)

- 本文針對成像聲納擴(kuò)展圖像動態(tài)范圍和增強(qiáng)圖像細(xì)節(jié)的需求,提出了一種基于開方運(yùn)算的動態(tài)范圍擴(kuò)展方法。基于課題組研制的多波束成像聲納原理樣機(jī)的研制,分析了數(shù)據(jù)動態(tài)范圍壓縮導(dǎo)致圖像細(xì)節(jié)丟失的原因及其對成像質(zhì)量的影響,采用JPL快速平方根近似算法改善了開方運(yùn)算FPGA實(shí)現(xiàn)過程的資源占用和系統(tǒng)延時。最后,對改進(jìn)設(shè)計方案進(jìn)行了實(shí)驗(yàn)驗(yàn)證,通過多波束成像聲納系統(tǒng)的消聲水池實(shí)驗(yàn)證明了本文動態(tài)范圍擴(kuò)展方法的有效性和可行性,系統(tǒng)成像質(zhì)量改善明顯,達(dá)到優(yōu)化設(shè)計的預(yù)期目標(biāo)。

- 關(guān)鍵字: 成像聲納 動態(tài)范圍 平方根 FPGA 波束成像 201505

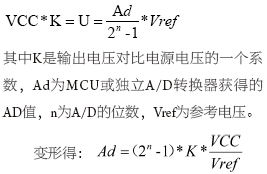

無運(yùn)放的權(quán)電阻網(wǎng)絡(luò)在單片機(jī)控制系統(tǒng)中的應(yīng)用(下)

- 接上篇 編程思路 對于電阻類數(shù)據(jù),常用的數(shù)表有電阻數(shù)表、AD數(shù)表。 1. 電阻數(shù)表,優(yōu)點(diǎn)是直觀,方便后期查驗(yàn),與電源電壓無關(guān);缺點(diǎn)和AD值之間需要額外的計算,占用系統(tǒng)時間。 2. AD數(shù)表,優(yōu)點(diǎn)是MCU只需做比較而無需乘除,與電源電壓無關(guān);缺點(diǎn)是不直觀,需要保存好原始的計算表格以備查驗(yàn)。 這里使用第二種AD數(shù)表,我們推導(dǎo)一下AD值與地址設(shè)置值之間的關(guān)系: 因?yàn)椴⒙?lián)電路和串聯(lián)電路都是線性電路,電源VCC的波動會直接導(dǎo)致輸出電壓波動,所以直接把VCC和Vref連接能

- 關(guān)鍵字: MCU PCB 電阻 AD數(shù)表 VCC

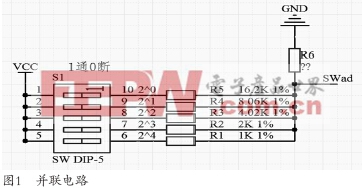

無運(yùn)放的權(quán)電阻網(wǎng)絡(luò)在單片機(jī)控制系統(tǒng)中的應(yīng)用(上)

- 前言 命題的起源是一款RS485從機(jī)設(shè)計過程中,需要給它提供一個手動設(shè)置從機(jī)地址的功能,市面上同類產(chǎn)品,一般是兩種做法。 一種是純軟件,通過設(shè)備的RS485端口,按廠家給出的通信協(xié)議,比如Modbus RTU,修改它作為從機(jī)地址的寄存器的值,有些要求重啟才生效。優(yōu)點(diǎn)是節(jié)省了PCB面積和相關(guān)的元器件,缺點(diǎn)是操作麻煩,需要客戶先搭建軟硬件環(huán)境,把設(shè)備地址修改完后再安裝到系統(tǒng)里。 另一種是硬件上提供了撥碼開關(guān),想修改地址時,撥成不同的地址組合就可以了。這種做法優(yōu)點(diǎn)是操作很簡單,不需要額外的

- 關(guān)鍵字: RS485 MCU PCB 單片機(jī) 電阻

基于FPGA的LZO實(shí)時無損壓縮的硬件設(shè)計

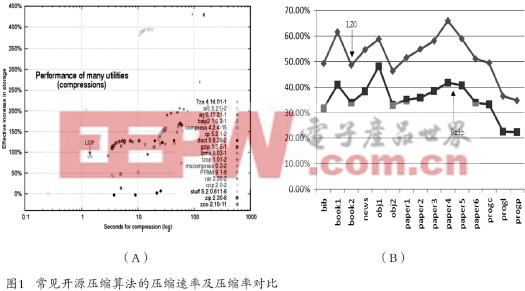

- 本文通過對多種壓縮算法作進(jìn)一步研究對比后發(fā)現(xiàn),LZO壓縮算法是一種被稱為實(shí)時無損壓縮的算法,LZO壓縮算法在保證實(shí)時壓縮速率的優(yōu)點(diǎn)的同時提供適中的壓縮率。如圖1(A)給出了Linux操作系統(tǒng)下常見開源壓縮算法的壓縮速率的測試結(jié)果,LZO壓縮算法速率極快;如圖1(B)給出了Gzip壓縮算法和LZO壓縮算法的壓縮率測試結(jié)構(gòu),從圖中可以看出,LZO壓縮算法可以提供平均約50%的壓縮率。 1 LZO壓縮算法基本原理分析 1.1 LZO壓縮算法壓縮原理 LZO壓縮算法采用(重復(fù)長度L,指回

- 關(guān)鍵字: LZO FPGA LZSS RAM 壓縮算法

e絡(luò)盟為亞太區(qū)推出全新系列PCB連接器助力新一代電子產(chǎn)品設(shè)計

- e絡(luò)盟日前宣布新增來自TE Connectivity、Molex、FCI、Harwin、Hirose 、JST、菲尼克斯及Samtec等全球領(lǐng)先供應(yīng)商的PCB連接器,進(jìn)一步豐富了已超過21萬種連接器的產(chǎn)品庫存。新增產(chǎn)品涵蓋壓接和焊接端子、D-Sub連接器、矩形電源連接器、接線端子塊,以及Mil-DTL-5015、83723、26482、26500等軍規(guī)級圓形連接器和適用于惡劣環(huán)境的(IP69K等級)圓形連接器。 新增PCB連接器系列包括板對板連接器、卡緣連接器、背板連接器、DIN 41612連接

- 關(guān)鍵字: e絡(luò)盟 PCB

使用FPGA實(shí)現(xiàn)靈活的USB Type-C接口控制

- 1 USB Type-C接口介紹 二十年前,第一代通用串行總線(Universal Serial Bus, USB 1.0)的出現(xiàn),為各自為政的電子行業(yè)通信標(biāo)準(zhǔn)注入了互通性。而最新發(fā)布的USB Type-C接口規(guī)范將USB技術(shù)提升到了一個新的高度,能夠滿足21世紀(jì)電子行業(yè)的需求,同時也將再一次改變計算機(jī)、消費(fèi)類電子產(chǎn)品以及移動設(shè)備之間的互連方式。輕薄、堅固、無需區(qū)分插頭方向的USB Type-C連接器拓展了由USB 3.1超速(SuperSpeed+)規(guī)范定義的各項(xiàng)功能,采用雙通道實(shí)現(xiàn)高達(dá)20

- 關(guān)鍵字: FPGA USB Type-C 充電器 嵌入式

基于FPGA的高可靠全自動加樣器

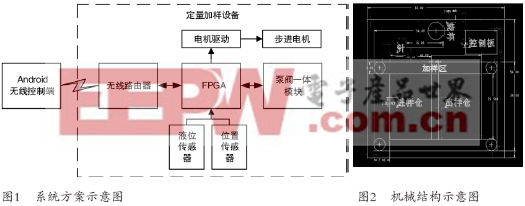

- 1 系統(tǒng)方案 智能加樣器系統(tǒng)以FPGA為控制核心,通過控制步進(jìn)電機(jī)的運(yùn)動,結(jié)合到位傳感器,控制整個設(shè)備機(jī)械平臺的正常運(yùn)轉(zhuǎn);通過處理液位傳感器信號和控制泵閥一體模塊,實(shí)現(xiàn)加樣功能;同時,采用無線網(wǎng)絡(luò)與安卓手機(jī)通訊,將安卓手機(jī)作為無線控制終端和數(shù)據(jù)顯示平臺。系統(tǒng)的設(shè)計方案如圖1所示。 為了提高系統(tǒng)加樣速率與效率,設(shè)計了以試管架作為加樣單位的加樣方式。如圖2所示,系統(tǒng)由步進(jìn)電機(jī)帶動機(jī)械推臂和行車,實(shí)現(xiàn)試管架在進(jìn)樣倉、加樣區(qū)與出樣倉之間的推動轉(zhuǎn)移,并在加樣區(qū)實(shí)現(xiàn)對試管的依次加樣。這種新型的加樣

- 關(guān)鍵字: FPGA 傳感器 液位探測 注射器 單片機(jī)

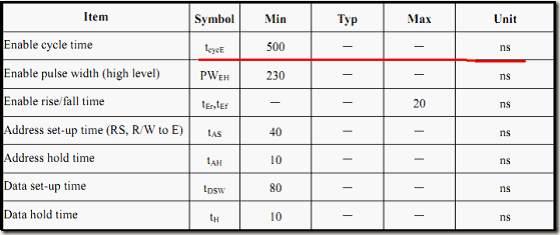

【從零開始走進(jìn)FPGA】 LCD1602 Hello World

- 前面說過,在C,C++等語言學(xué)習(xí)中,“Hello World”將會是第一個學(xué)習(xí)的代碼,但是在FPGA中由于電路驅(qū)動的復(fù)雜性,與單片機(jī)雷同,我們無法在電腦上實(shí)現(xiàn)“Hello World”的顯示,而必須依靠相關(guān)硬件。因此我們不得不在一定的基礎(chǔ)上,才能講解關(guān)于LCD1602字符液晶的驅(qū)動,以及Hello World的顯示。 雷同于前面MCU按鍵消抖動移植代碼,此處也可以移植MCU LCD1602驅(qū)動代碼。本例程不是Bingo原創(chuàng),是按照網(wǎng)友“

- 關(guān)鍵字: FPGA LCD1602

fsp:fpga-pcb介紹

您好,目前還沒有人創(chuàng)建詞條fsp:fpga-pcb!

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fsp:fpga-pcb的理解,并與今后在此搜索fsp:fpga-pcb的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司