- 作為FPGA工程師來說,碰到新的問題是設計中最常見的事情了,技術發展趨勢日新月異,所以經常會有新的概念,新的需求,新的設計等待去實現。不是每個通過BAIDU或者GOOGLE都有答案。

因此,新的設計經常會有,那如何實現?

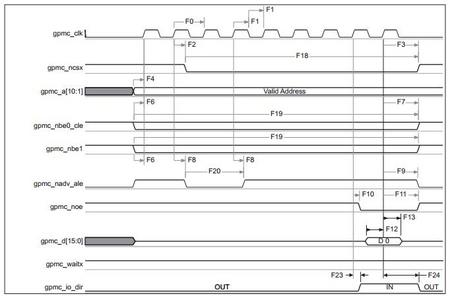

假設,FPGA需要設計一個接口模塊,那我們就需要了解一下幾個問題:

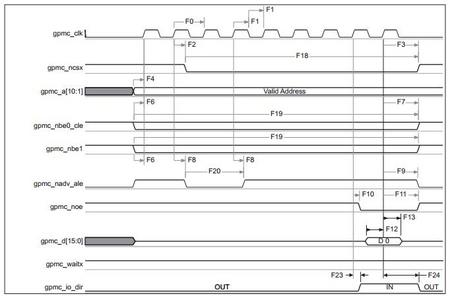

(1) 同步接口還是異步接口模塊;

(2) 有哪些信號,功能是什么?

(3) 信號之間時序關系是什么?

(4) 傳遞的效率能夠達到多少;

(5) 等等!

誰會給予這些答

- 關鍵字:

FPGA 測試 接口

- 寫在coding之前的那些鐵律

(1)注釋: 好的代碼首先必須要有注釋,注釋至少包括文件注釋,端口注釋,功能語句注釋。

文件注釋:文件注釋就是一個說明文:這通常在文件的頭部注釋,用于描述代碼為那個工程中,由誰寫的,日期是多少,功能描述,有哪些子功能,及版本修改的標示。這樣不論是誰,一目了然。即使不寫文檔,也能知道大概。

接口描述:module的接口信號中,接口注釋描述模塊外部接口,例如AHB接口,和SRAM接口等等。這樣讀代碼的人即可能夠判斷即模塊將AHB接口信號線轉換成SRAM接口

- 關鍵字:

FPGA coding 時序

- 1 項目背景

1.1 研究背景

LCD顯示屏的應用越來越廣,數量越來越多。LCD顯示屏應用廣泛,無處不在。小到家庭各種電器設備,大到軍事設備。更常見是用于各種公共場合如體育館、廣場等商業用途。給我們傳遞一種更為直觀、生動的信息。從此我們的生活發生了巨大改變。巨大的應用巨大的市場帶來了巨大的商機。傳統的顯示器大多采用控制系統與顯示界面集成在一起的方案,不便于實時管理與有效維護,不便于及時更新;也不便于人親臨惡劣的工作環境下進行人為操控。LED顯示屏用戶迫切需要實現對LED顯示屏的遠程控制。

- 關鍵字:

FPGA LCD Microblaze

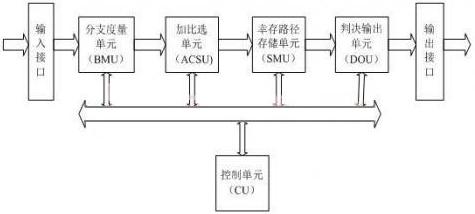

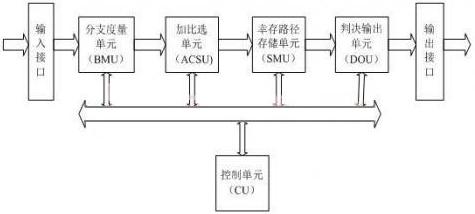

- 卷積碼是廣泛應用于衛星通信、無線通信等各種通信系統的信道編碼方式。Viterbi算法是一種最大似然譯碼算法。在碼的約束度較小時,它比其它概率譯碼算法效率更高、速度更快,譯碼器的硬件結構比較簡單。隨著可編程邏輯技術的不斷發展,其高密度、低功耗、使用靈活、設計快速、成本低廉、現場可編程和反復可編程等特性,使FPGA逐步成為Viterbi譯碼器設計的最佳方法。項目目的是用FPGA實現一個Viterbi譯碼器。

一、譯碼器功能分析

譯碼器是一種具有“翻譯”功能的邏輯電路,這

- 關鍵字:

FPGA Viterbi 譯碼器

- 項目研究的目的和主要研究內容

研究目的

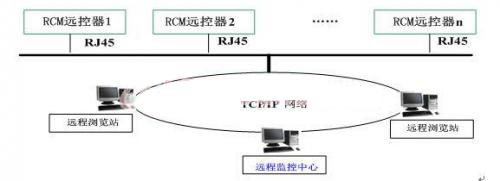

為了遠程對現場進行設備管理和環境監控,并簡化現場監控設備,有效地提高整個系統的穩定性和安全性。擬開發一款遠程控制器,簡稱RCM遠控器。該遠控器將集現場數據采集、多種通信協議轉換、故障告警、應急控制、智能聯動、內嵌WEB配置頁等多項功能。

主要研究內容

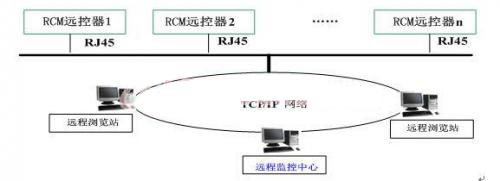

1.遠程監控系統

遠程監控系統總體結構(如圖1所示),其中主要研究內容為RCM遠控器。

?

圖 1

遠控器通過RJ45與TCP/IP網絡開放式網絡相

- 關鍵字:

FPGA DSP RCM

- 引言

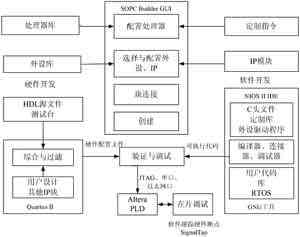

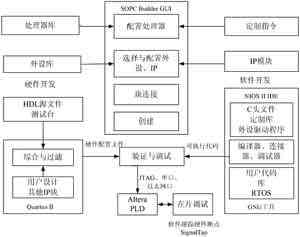

在工業現場中,大多的通信設備是通過加裝通信模塊來實現的,而大多的通信模塊的處理器采用ARM核。隨著微電子學和計算機科學的迅速發展,電子系統已經從電路板級系統集成發展成為包括ASIC、FPGA和嵌入式系統的多種模式。SOPC由于集成了硬核或軟核CPU、DSP、存儲器、外圍I/O及可編程邏輯模塊,在設計和應有的靈活性及其成本方面有較大的優勢。

NIOSⅡ系列處理器是Altera公司的第二代FPGA嵌入式處理器。同前一代軟核的CPU相比,NIOSⅡ的性能得到很大提高,體積更小,其最大處理能

- 關鍵字:

NIOS II BCMO4 藍牙

- 1設計摘要

1.1項目背景

漢字作為非字母化、非拼音化的文字,在當今高度信息化的社會里,如何快速高效地將漢字輸入計算機,已成為影響人機交流信息效率的一個重要瓶頸。目前,漢字輸入主要分為人工鍵盤輸入和機器自動識別輸入兩種,其中人工鍵入速度慢且勞動強度大。自動識別輸入分為語音識別和漢字識別兩種,其中漢字識別是將漢字點陣圖形轉換成電信號,然后輸入給數字信號處理器或計算機進行處理,依據一定的分類算法在漢字字符集合中識別出與之相匹配的漢字。因此,研究脫機手寫體漢字識別的目的就是解決漢字信息如何高速輸

- 關鍵字:

FPGA 神經網絡 漢字識別

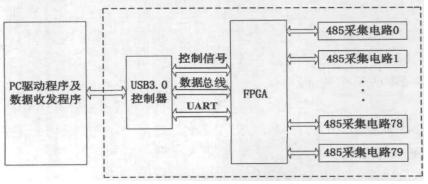

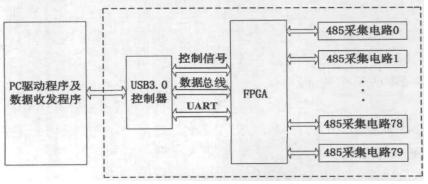

- 多串口數據通信技術主要研究數據的多串口采集、存儲和處理。由于串口通信技術的廣泛應用,使得多串口采集卡一直是研究的熱點,從早期的基于PCI總線的多串口數據采集卡到后來的基于USB的多串口數據采集卡,以及現在的基于USB3.0的多串口數據采集卡。

PCI采集卡由于使用不方便,逐漸被淘汰,目前USB傳輸系統被廣泛應用。USB2.0理論傳輸速度為480Mb/s,而USB3.0的傳輸速率可高達5Gb/s,且在USB2.0的基礎上又增加了超高速傳輸模式。本文設計的系統中有80個485傳輸通道,每個通道的速率

- 關鍵字:

USB3.0 FPGA PCI

- 廣東高云半導體科技股份有限公司(以下簡稱“高云半導體”)今日宣布推出擁有完全自主知識產權的現場可編程門陣列(FPGA)朝云™產品系列。可廣泛用于通信網絡、工業控制、工業視頻、服務器、消費電子等領域,幫助用戶降低開發風險,迅速克服產品上市時間帶來的挑戰。

朝云™產品系列在目前FPGA市場上處于中密度范圍,邏輯單元從18K LUT到100K LUT。其中有兩個家族產品,分別為GW2A和GW3S。前者采用臺積電(TSMC)的55nm工藝,后者采用臺積電的

- 關鍵字:

高云 FPGA GW2A

- 2014年10月29日 上海IC-China訊,廣東高云半導體科技股份有限公司(簡稱高云半導體)今日召開新產品發布會,宣布推出擁有我國完全自主知識產權的三大產品計劃:

現場可編程門陣列(FPGA)朝云™產品系列;

現場可編程門陣列(FPGA)云源™設計軟件;

基于現場可編程門陣列(FPGA)的IP軟核平臺—星核計劃。

擁有完全自主知識產權的現場可編程門陣列(FPGA)朝云™產品系列。

- 關鍵字:

FPGA 高云 朝云

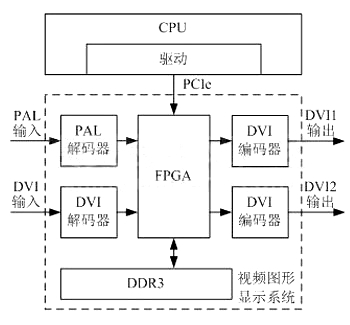

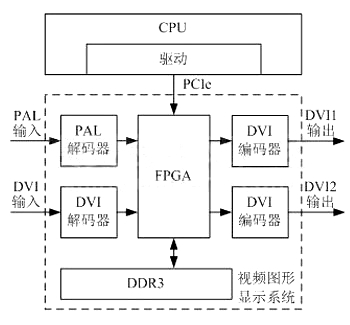

- 隨著航空電子技術的不斷發展,現代機載視頻圖形顯示系統對于實時性等性能的要求日益提高。常見的系統架構主要分為三種:

(1)基于GSP+VRAM+ASIC的架構,優點是圖形ASIC能夠有效提高圖形顯示質量和速度,缺點是國內復雜ASIC設計成本極高以及工藝還不成熟。

(2)基于DSP+FPGA的架構,優點是,充分發揮DSP對算法分析處理和FPGA對數據流并行執行的獨特優勢,提高圖形處理的性能;缺點是,上層CPU端將OpenGL繪圖函數封裝后發給DSP,DSP拆分后再調用FPGA,系統的集成度不高

- 關鍵字:

FPGA DSP ASIC

- 廣東高云半導體科技股份有限公司(簡稱高云半導體)在IC-China上召開新產品發布會,宣布推出擁有我國完全自主知識產權的現場可編程門陣列(FPGA)朝云?產品系列、現場可編程門陣列(FPGA)云源?設計軟件、基于現場可編程門陣列(FPGA)的IP軟核平臺——“星核計劃”三大產品。

三大系列產品詳細情況如下:

1.擁有完全自主知識產權的現場可編程門陣列(FPGA)朝云?產品系列

朝云?產品系

- 關鍵字:

高云 FPGA

- 為加速芯片和電子系統創新而提供軟件、知識產權(IP)及服務的全球性領先供應商新思科技公司日前宣布:已與廣東高云半導體科技股份有限公司(Gowin Semiconductor)就Synopsys SynplifyPro FPGA綜合工具簽署一項多年OEM協議。該協議將使高云的客戶能夠改善邏輯綜合運行時間,并為GowinGW2A/3S FPGA系列實現更高質量的時序、面積及功耗設計。高云半導體已與Synopsys合作把Synplify Pro集成到用于其GW2A/3S FPGA系列的GOWINTM設計套件

- 關鍵字:

Synopsys FPGA DSP

- 在FPGA內部資源中,RAM是較為常用的一種資源。

通常實例化RAM中,一種使用為BLOCK RAM 也就是塊RAM 。另外資源可以通過寄存器搭,也就是分布式RAM。前者一般用于提供較大的存儲空間,后者則提供小的存儲空間。

在實際應用過程中,一般使用的包括,單端口、雙端口RAM,ROM等形式等不同的形式。 實際應用中FIFO也是利用RAM和邏輯一起實現的。

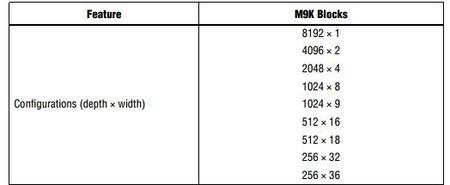

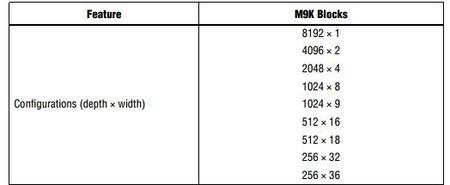

對于一塊RAM中,其能夠例化的深度是有限的。例如cyclone4的RAM9k中可以例化的資源如下所示:

?

- 關鍵字:

FPGA RAM ROM

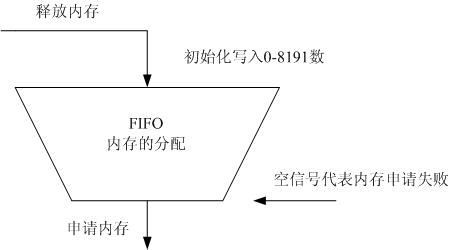

- FIFO在FPGA設計中除了上篇所介紹的功能之外, 還有以下作為以下功能使用:

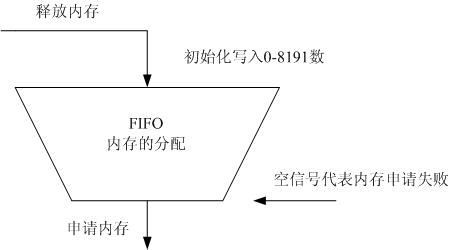

(1) 內存申請

在軟件設計中,使用malloc()和free()等函數可以用于內存的申請和釋放。特別是在有操作系統的環境下,可以保證系統的內存空間被動態的分配和使用,非常的方便。如果在FPGA內部實現此動態的內存分配和申請,相對來說較為復雜,例如某些需要外部數據存儲且需動態改變的應用需求下,需要對FPGA外部DDR(或SRAM等)的存儲空間,進行動態的分配和釋放。通過使用FIFO作為內存分配器,雖然比不上軟件

- 關鍵字:

FPGA FIFO SRAM

fpga-nios介紹

您好,目前還沒有人創建詞條fpga-nios!

歡迎您創建該詞條,闡述對fpga-nios的理解,并與今后在此搜索fpga-nios的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473