fpga soc 文章 最新資訊

解析高速ADC和DAC與FPGA的配合使用

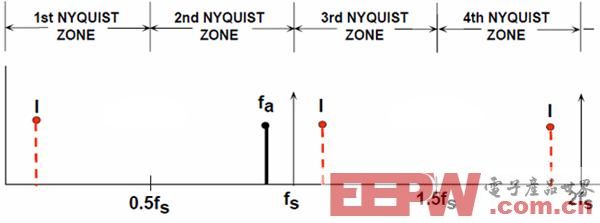

- 許多數(shù)字處理系統(tǒng)都會使用FPGA,原因是FPGA有大量的專用DSP以及block RAM資源,可以用于實現(xiàn)并行和流水線算法。因此,通常情況下,F(xiàn)PGA都要和高性能的ADC和DAC進行接口,比如e2v EV10AQ190低功耗四通道10-bit 1.25 Gsps ADC和EV12DS130A內(nèi)建4/2:1 MUX的低功耗12-bit 3 Gsps DAC。 通常情況下,這些轉(zhuǎn)換器的采樣率都達到了GHz的級別。對工程師團隊來說,除了混合信號電路板布局之外,理解和使用這些高性能的設(shè)備也是一個挑戰(zhàn)。

- 關(guān)鍵字: ADC DAC FPGA

一種于FPGA的多通道頻率測量系統(tǒng)設(shè)計

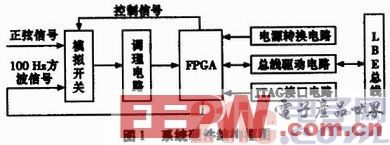

- 摘要:設(shè)計了一種多通道頻率測量系統(tǒng)。系統(tǒng)由模擬開關(guān)、信號調(diào)理電路、FPGA、總線驅(qū)動電路構(gòu)成,實現(xiàn)對頻率信號的分壓、放大、濾波、比較、測量,具備回路自測試功能,可與主設(shè)備進行數(shù)據(jù)交互,具有精度高、可擴展、易維護的特點,有一定的工程應(yīng)用價值。 頻率測量電路是很多檢測與控制系統(tǒng)的重要組成部分,在航空機載計算機領(lǐng)域具有廣泛的應(yīng)用環(huán)境。隨著檢測與控制系統(tǒng)復(fù)雜程度的提高,頻率測量電路也被提出了新的要求,例如多通道實時采集、高精度測量等。FPGA的特點是完全由用戶通過軟件進行配置和編程,從而完成某種特定的功

- 關(guān)鍵字: FPGA 頻率測量 可編程邏輯

一款四象限 DC/DC 開關(guān)穩(wěn)壓器的實現(xiàn)

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: DC/DC轉(zhuǎn)換器 FPGA NMOS 開關(guān)穩(wěn)壓器

基于FPGA的大功率數(shù)字音頻系統(tǒng)設(shè)計

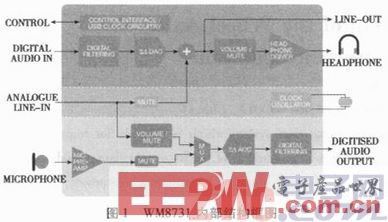

- 摘要:音頻編解碼芯片WM8731因其高性能、低功耗等優(yōu)點在很多音頻產(chǎn)品中得到了廣泛應(yīng)用。本文提出了WM8731與FPGA的音頻編解碼系統(tǒng),并嵌入大功率D類功放技術(shù)作為音頻系統(tǒng)的功率放大應(yīng)用,使得本系統(tǒng)效率高,體積小,音質(zhì)高,性能顯著。 隨著FPGA技術(shù)的迅速發(fā)展,大規(guī)模集成可編程邏輯陣列越來越普遍。在現(xiàn)代電子技術(shù)領(lǐng)域表現(xiàn)出明顯技術(shù)領(lǐng)先優(yōu)勢。本文為一個基于FPGA技術(shù)的嵌入式數(shù)字音頻編解碼系統(tǒng)的設(shè)計方案,極大地提高了系統(tǒng)的集成度和穩(wěn)定性,同時降低了產(chǎn)品開發(fā)成本,提高了系統(tǒng)設(shè)計效率。另外功率放大電路

- 關(guān)鍵字: FPGA 音頻系統(tǒng) 數(shù)字功放

Cadence在上海成功舉辦2014年使用者大會CDNLive 2014!

- 全球電子設(shè)計創(chuàng)新領(lǐng)先公司Cadence設(shè)計系統(tǒng)公司 (Cadence Design Systems, Inc) 在上海浦東嘉里大酒店舉辦年度CDNLive使用者大會,會議集聚了Cadence的技術(shù)用戶、開發(fā)者、業(yè)界專家與行業(yè)媒體700多人,Cadence工具的開發(fā)專家和使用者們面對面分享重要設(shè)計與驗證問題的解決經(jīng)驗,探討高級晶片、SoC和系統(tǒng)的技術(shù)潮流趨勢。 5號早上,Cadence公司副總裁兼中國區(qū)總經(jīng)理劉國軍先生首先代表公司歡迎業(yè)界客戶、合作伙伴、專家學(xué)者及媒體朋友的到來。Cadence總裁

- 關(guān)鍵字: Cadence CDNLive SoC

一種于FPGA的高速導(dǎo)航解算系統(tǒng)設(shè)計與實現(xiàn)

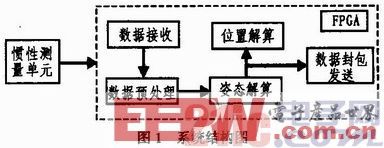

- 摘要:針對現(xiàn)有小型無人機導(dǎo)航系統(tǒng)的解算速度慢、多處理器核心臃腫可靠性差的缺點,實現(xiàn)了一種僅使用單一FPGA作為數(shù)據(jù)處理核心的小型高速導(dǎo)航解算系統(tǒng)。該系統(tǒng)對飛機運動方程組和導(dǎo)航方程組進行并行化分解,對相互獨立的中間變量進行并行計算,使得單個運算周期能夠同時進行6次浮點運算,在不盲目增加硬件消耗的條件下有效提高了解算速度。仿真和實驗結(jié)果表明系統(tǒng)能夠高效地進行導(dǎo)航信息解算,在小型無人機的導(dǎo)航控制領(lǐng)域有重要的工程應(yīng)用價值。 導(dǎo)航解算是小型無人機導(dǎo)航控制的基礎(chǔ),小型無人機機動性強,為了完成自主導(dǎo)航任務(wù),必

- 關(guān)鍵字: FPGA 姿態(tài)解算 導(dǎo)航解算

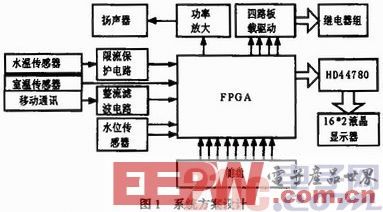

一款基于FPGA的智能熱水器設(shè)計

- 摘要:傳統(tǒng)電熱水器系統(tǒng)大多采用單片機作為控制核心,僅具有加熱和保溫功能,水溫不可見,水量不易控制,大多熱水器在保溫時采用開關(guān)控制,給電力系統(tǒng)帶來巨大沖擊。本系統(tǒng)選用現(xiàn)場可編程邏輯器件Actel Fusion系列FPGA作為控制核心,充分利用其內(nèi)部模數(shù)混合的特點實現(xiàn)水溫數(shù)字可視化、可預(yù)約時間等等功能,運用PID算法實現(xiàn)水的加熱和保溫,使電力系統(tǒng)受到很小的沖擊,且該系統(tǒng)具有安全可靠、節(jié)能、高效能、性能穩(wěn)定、簡易操作的特性。 隨著社會的進步與發(fā)展,家庭生活的標(biāo)準(zhǔn)也在不斷提高,人們更加追求家庭生活的高度

- 關(guān)鍵字: 模數(shù)混合 FPGA 低功耗 PID算法

復(fù)位設(shè)計中的結(jié)構(gòu)性缺陷及解決方案

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: 復(fù)位設(shè)計 SoC 寄存器

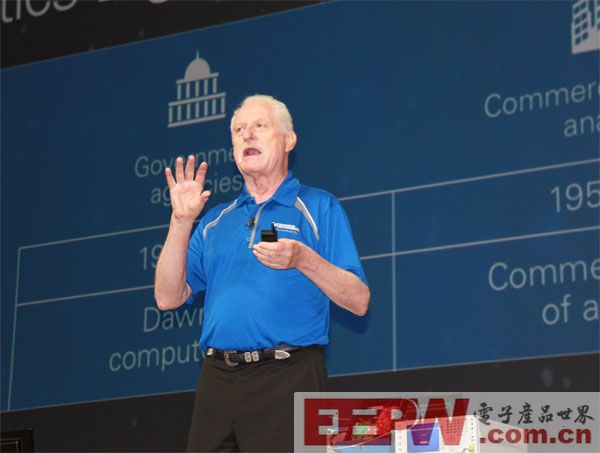

NI Week第二天:重量級產(chǎn)品登場,企業(yè)級客戶受寵

- NI Week 2014進入第二天,今天的主題演講環(huán)節(jié)重點是推介LabVIEW 2014的新特性,以及NI的各種重量級新產(chǎn)品和新方案的發(fā)布。 在主題演講開始之前,NI市場合作副總裁Ray Almgren首先發(fā)布了NI公司的全新口號,也是今年的NI Week的一個主題,就是You and NI will,強調(diào)NI會在智能交通、工業(yè)自動化、無線技術(shù)、智能電網(wǎng)、新能源多個熱點的技術(shù)應(yīng)用領(lǐng)域,與客戶一起去推動技術(shù)的進步。 NI創(chuàng)始人 CEO Dr T 年逾70的Dr T依然精神矍鑠的為所

- 關(guān)鍵字: NI Week PXIe-5668R VSA FPGA

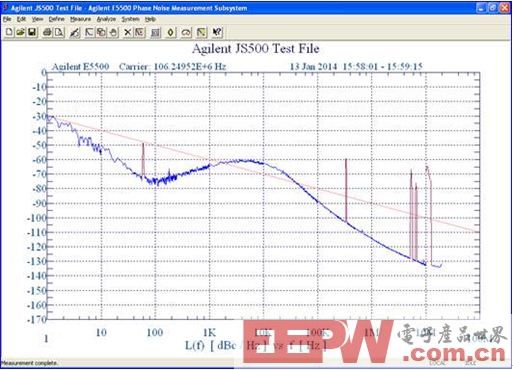

探討如何為定時應(yīng)用選擇合適的PLL振蕩器

- 十幾年前,頻率控制行業(yè)推出了基于鎖相環(huán)(PLL)的振蕩器,這是一項開拓性創(chuàng)新技術(shù),采用了傳統(tǒng)晶體振蕩器(XO)所沒有的多項特性。憑借內(nèi)部時鐘合成器IC技術(shù),基于PLL的XO可編程來支持更寬廣的頻率范圍。這一突破消除了為在特定頻率實現(xiàn)共振而切割和加工石英所需的材料加工工藝步驟。這一創(chuàng)新也使得對基于PLL的XO進行頻率編程成為可能并且實現(xiàn)極短交貨周期。 鑒于傳統(tǒng)振蕩器交貨周期可能接近14周或更長,許多硬件設(shè)計人員渴望利用可編程振蕩器獲得顯著的交貨周期優(yōu)勢。不幸的是,嚴(yán)重的問題發(fā)生了。一些已經(jīng)從傳統(tǒng)X

- 關(guān)鍵字: 振蕩器 PLL SoC

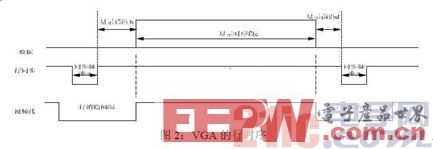

基于FPGA/CPLD的VGA顯示系統(tǒng)設(shè)計

- VGA(視頻圖形陣列Video Graphics Array)是IBM在1987年隨PS/2機一起推出的一種視頻傳輸標(biāo)準(zhǔn),具有分辨率高、顯示速率快、顏色豐富等優(yōu)點,在彩色顯示器領(lǐng)域得到了廣泛的應(yīng)用。 目前 VGA技術(shù)的應(yīng)用還主要基于 VGA顯示卡的,而在一些既要求顯示彩色高分辨率圖像又不使用計算機的設(shè)備上,VGA技術(shù)的應(yīng)用卻很少。本文對基于 FPGA/CPLD的嵌入式 VGA顯示的實現(xiàn)方法進行了研究。 基于 FPGA/CPLD的嵌入式 VGA顯示系統(tǒng),可以在不使用 VGA顯示卡的情況下實現(xiàn)

- 關(guān)鍵字: FPGA CPLD VGA

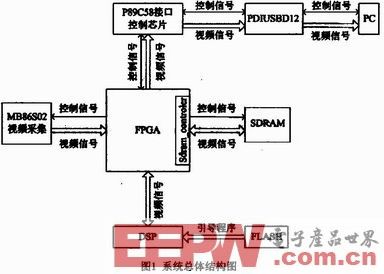

基于FPGA+DSP的視頻處理系統(tǒng)設(shè)計

- 摘要:實時圖像處理技術(shù)在工業(yè)、醫(yī)學(xué)、軍事和商業(yè)等領(lǐng)域有廣泛的應(yīng)用。基于FPGA+DSP架構(gòu)的視頻處理系統(tǒng)充分發(fā)揮了各自器什的長處,不儀設(shè)計周期短,開發(fā)費用低,而且設(shè)計靈活,更改方便,功耗較低,便于實現(xiàn)系統(tǒng)的小型化。因此對基與FPGA+DSP架構(gòu)的視頻處理系統(tǒng)進行研究和設(shè)計具有重要的意義。 0 引言 本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實時視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適

- 關(guān)鍵字: FPGA DSP SDRAM

一種基于FPGA的流水線FIR濾波器設(shè)計

- 摘要:有限沖擊響應(yīng)(FIR)濾波器是數(shù)字通信系統(tǒng)中常用的基本模塊。文章設(shè)計了一種流水結(jié)構(gòu)的FIR濾波器,通過FPGA對其進行硬什加速控制。仿真結(jié)果驗證了所設(shè)計的FIR流水結(jié)構(gòu)濾波器功能的正確性。 0 引言 隨著數(shù)字通信技術(shù)的快速發(fā)展,高質(zhì)量的信息處理對濾波器的性能和資源占有量提出了更高的要求。有限沖擊響應(yīng)(FIR)數(shù)字有限沖激響應(yīng)濾波器在語音、譜分析等數(shù)字信號處理領(lǐng)域有著廣泛的應(yīng)用,是信號處理系統(tǒng)中重要的組成部分,其性能往往對整個系統(tǒng)的性能和功耗產(chǎn)生至關(guān)重要的影響。因此,如何最大程度地優(yōu)化

- 關(guān)鍵字: FPGA FIR濾波器 流水線

fpga soc介紹

您好,目前還沒有人創(chuàng)建詞條fpga soc!

歡迎您創(chuàng)建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司