fpga soc 文章 最新資訊

10個心率監(jiān)控裝置設計方案,包括電路圖原理圖等

- 心率監(jiān)控器是一款用于監(jiān)測人體心跳速率的器件。心率的單位是bpm(每分鐘心跳數(shù))。人體的心跳速率根據(jù)其日常身體活動、睡眠和基本健康狀況的不同而有所差別。本文為大家介紹幾種心率計及心率監(jiān)測系統(tǒng)的設計,供大家使用參考。 基于EFM32TG840的便攜式心率計的設計方案 在消費電子領域,便攜式電子產(chǎn)品由于體積小、質量輕的特點越來越受到消費者的喜愛,已成為人們生活中不可缺少的部分。基于這個思路,我們設計了一款便攜式心率計,它可以替代用脈搏聽診器等進行測量的傳統(tǒng)方法,使用非常方便。 一種便攜式單

- 關鍵字: FPGA VHDL

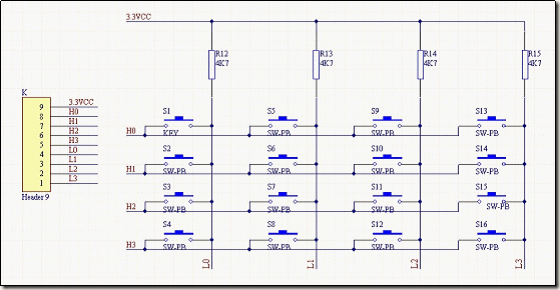

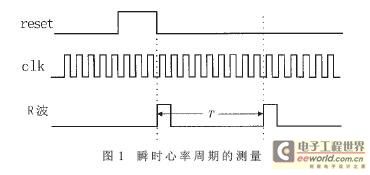

基于FPGA的數(shù)字式心率計系統(tǒng)的設計實現(xiàn)

- 心率計是常用的醫(yī)學檢查設備,實時準確的心率測量在病人監(jiān)控、臨床治療及體育競賽等方面都有著廣泛的應用。心率測量包括瞬時心率測量和平均心率測量。瞬時心率不僅能夠反映心率的快慢。同時能反映心率是否勻齊;平均心率雖只能反映心率的快慢,但記錄方便,因此這兩個參數(shù)在測量時都是必要的。 測量心率有模擬和數(shù)字兩種方法。模擬方法是在給定的時間間隔內計算R波(或脈搏波)的脈沖個數(shù),然后將脈沖計數(shù)乘以一個適當?shù)某?shù)測量心率的。這種方法的缺點是測量誤差較大、元件參數(shù)調試困難、可靠性差。數(shù)字方法是先測量相鄰R波之間的時間

- 關鍵字: FPGA 心率計

Cadence推出Innovus設計實現(xiàn)系統(tǒng)周轉時間減少最高達10倍,并交付最佳品質的結果

- Cadence(Cadence Design Systems, Inc. )今天發(fā)布Cadence® Innovus™ 設計實現(xiàn)系統(tǒng),這是新一代的物理設計實現(xiàn)解決方案,使系統(tǒng)芯片(system-on-chip,SoC)開發(fā)人員能夠在加速上市時間的同時交付最佳功耗、性能和面積(PPA)指標的的設計。Innovus設計實現(xiàn)系統(tǒng)由具備突破性優(yōu)化技術所構成的大規(guī)模的并行架構所驅動,在先進的16/14/10納米FinFET工藝制程和其他成熟的制程節(jié)點上通常能提升10%到20%的功耗、性能和面

- 關鍵字: Cadence SoC

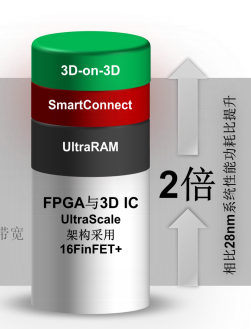

僅有16nm還不夠,Xilinx在下一代FPGA/SoC中加入多種猛料

- 2月底,Xilinx發(fā)布了下一代16nm產(chǎn)品特點的新聞:《Xilinx憑借新型存儲器、3D-on-3D 和多處理SoC技術在16nm繼續(xù)遙遙領先》(http://www.104case.com/article/270122.htm),大意是說,Xilinx新的16nm FPGA和SoC中,將會采用新型存儲器UltraRAM, 3D晶體管(FinFET)和3D封裝,Zynq會出多處理器產(chǎn)品MPSoC,因此繼28nm和20nm之后,繼續(xù)在行業(yè)中保持領先,打破了業(yè)內這樣的規(guī)則:Xilinx和競爭對手在工藝上

- 關鍵字: Xilinx FPGA

采用Nios的電能質量監(jiān)測系統(tǒng)解決方案

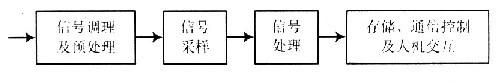

- 在電力系統(tǒng)中,要實現(xiàn)對電能質量各項參數(shù)的實時監(jiān)測和記錄,必須對電能進行高速的采集和處理,尤其是針對電能質量的各次諧波的分析和運算,系統(tǒng)要完成大量運算處理工作,同時系統(tǒng)還要實現(xiàn)和外部系統(tǒng)的通信、控制、人機接口等功能。而電能質量監(jiān)測系統(tǒng)大多以微控制器或(與)DSP為核心的軟硬件平臺結構以及相應的設計開發(fā)模式,存在著處理能力不足、可靠性差、更新?lián)Q代困難等弊端。本文將SoPC技術應用到電力領域,在FPGA中嵌入了32位NiosⅡ軟核系統(tǒng)。可實現(xiàn)對電能信號的采集、處理、存儲與顯示等功能,實現(xiàn)了實時系統(tǒng)的要求。

- 關鍵字: FPGA NiosⅡ

電能質量監(jiān)測系統(tǒng)信號采集模塊控制器IP核設計

- 隨著可編程邏輯器件的不斷進步和發(fā)展,F(xiàn)PGA在嵌入式系統(tǒng)中發(fā)揮著越來越重要的作用。本文介紹的在電能質量監(jiān)測系統(tǒng)中信號采集模塊控制器的 IP核,是采用硬件描述語言來實現(xiàn)的。首先它是以ADS8364芯片為控制對象,結合實際電路,將6通道同步采樣的16位數(shù)據(jù)存儲到FIFO控制器。當FIFO 控制器存儲一個周期的數(shù)據(jù)后,產(chǎn)生一個中斷信號,由PowerPC對其進行高速讀取。這樣能夠減輕CPU的負擔,不需要頻繁地對6通道的采樣數(shù)據(jù)進行讀取,節(jié)省了CPU運算資源。 1 ADS8364芯片的原理與具體應用

- 關鍵字: FPGA 信號采集

Xilinx將推出16nm的FPGA和SoC,融合存儲器、3D-on-3D和多處理SoC技術

- 賽靈思公司 (Xilinx+)日前宣布,其16nm UltraScale+? 系列FPGA、3D IC和MPSoC憑借新型存儲器、3D-on-3D和多處理SoC(MPSoC)技術,再次實現(xiàn)了領先的價值優(yōu)勢。此外,為實現(xiàn)更高的性能和集成度,UltraScale+系列還采用了全新的互聯(lián)優(yōu)化技術——SmartConnect。這些新的器件進一步擴展了賽靈思的UltraScale產(chǎn)品系列 (現(xiàn)從20nm 跨越至 16nm FPGA、SoC 和3D IC器件),同時利用臺積電公

- 關鍵字: 賽靈思 FPGA SoC UltraScale 201503

fpga soc介紹

您好,目前還沒有人創(chuàng)建詞條fpga soc!

歡迎您創(chuàng)建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對fpga soc的理解,并與今后在此搜索fpga soc的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司