EEPW首頁(yè) >>

主題列表 >>

arm+fpga

arm+fpga 文章 最新資訊

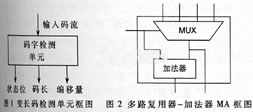

基于FPGA的并行可變長(zhǎng)解碼器的實(shí)現(xiàn)技術(shù)

- 可變長(zhǎng)編碼(VLC)是一種無(wú)損熵編碼,它廣泛應(yīng)用于多媒體信息處理等諸多領(lǐng)域。在H.261/263、MPEG1/2/3等國(guó)際標(biāo)準(zhǔn)中,VLC占有重要地位。VLC的基本思想是對(duì)一組出現(xiàn)概率各不相同的信源符號(hào),采用不同長(zhǎng)度的碼字表示,對(duì)出現(xiàn)概率高的信源符號(hào)采用短碼字,對(duì)出現(xiàn)概率低的信源符號(hào)采用長(zhǎng)碼字。Huffman編碼是一種典型的VLC,其編碼碼字的平均碼長(zhǎng)非常接近于數(shù)據(jù)壓縮的理論極限——熵。 可變長(zhǎng)解碼(VLD)是VLC的逆過(guò)程,它從一組連續(xù)的碼流中提取出可變長(zhǎng)碼字,并將之轉(zhuǎn)換

- 關(guān)鍵字: VLD 串行解碼 FPGA

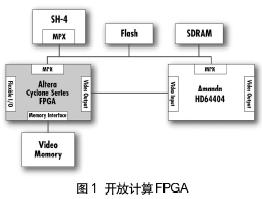

采用FPGA協(xié)處理器優(yōu)化汽車信息娛樂(lè)和信息通信系統(tǒng)(04-100)

- 集成了數(shù)據(jù)通信,定位服務(wù)和視頻娛樂(lè)的高端汽車信息娛樂(lè)系統(tǒng)需要高性能的可編程處理技術(shù),其最佳實(shí)現(xiàn)方法是在主流汽車信息通信系統(tǒng)構(gòu)架中集成FPGA協(xié)處理器。本文講述汽車娛樂(lè)系統(tǒng)的需求,討論主流系統(tǒng)構(gòu)架,以及FPGA協(xié)處理器是如何集成到軟硬件體系中,以滿足高性能處理、靈活性和降低成本的要求。 娛樂(lè)電子消費(fèi)已經(jīng)成為區(qū)分豪華轎車的標(biāo)志之一,推動(dòng)了汽車性能的快速發(fā)展,設(shè)計(jì)者必須在性能,成本和靈活性上進(jìn)行綜合考慮。高端應(yīng)用包括衛(wèi)星電話,后座娛樂(lè),導(dǎo)航,各種音頻回放,語(yǔ)音合成、識(shí)別以及其他新的應(yīng)用。 帶動(dòng)汽

- 關(guān)鍵字: FPGA 汽車娛樂(lè)系統(tǒng)

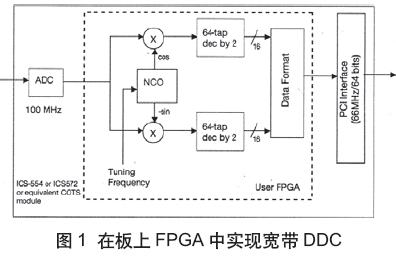

FPGA基軟件無(wú)線電(04-100)

- 軟件無(wú)線電技術(shù)給正在開(kāi)發(fā)無(wú)線電架構(gòu)的工程師帶來(lái)力量。編程中頻(IF)、帶寬、調(diào)制、編碼模式和其他無(wú)線電功能的能力廣泛引起注意。除了提供所有這些靈活性外,軟件無(wú)線電必須改善靈敏度,動(dòng)態(tài)范圍和鄰信道抑制性能。軟件無(wú)線電仍然是無(wú)線電,但它必須比被正在替代的通常無(wú)線電執(zhí)行的更好。 現(xiàn)場(chǎng)可編程陣列(FPGA)技術(shù)先進(jìn)之處在于緊湊的占位空間能夠高速處理,同時(shí)也保持軟件無(wú)線電技術(shù)的靈活性和可編程性。FPGA在高速、計(jì)算密集、可重新配置應(yīng)用(FFT、FIR和其他乘法—累加運(yùn)算)中是受歡迎的。從FPG

- 關(guān)鍵字: FPGA 無(wú)線電

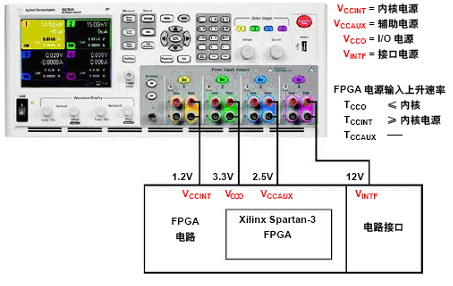

FPGA 電路設(shè)計(jì): 如何應(yīng)對(duì)電源相關(guān)問(wèn)題的挑戰(zhàn)

- 引言 在設(shè)計(jì)可編程門陣列(FPGA)電路時(shí),必須極端重視電源問(wèn)題,從而使最終產(chǎn)品能在所有可能的條件下無(wú)缺陷工作并處于最優(yōu)狀態(tài)。FPGA 電路電源有兩項(xiàng)需考慮的問(wèn)題: FPGA 電路上電要求和電路功耗分析。這篇文章針對(duì)這兩方面的要求,討論您可能遇到的問(wèn)題,以及解決方案。 目前FPGA電路設(shè)計(jì)所面臨的問(wèn)題 FPGA電路通常需要多路電源輸入。為優(yōu)化開(kāi)機(jī)時(shí)的電流拖曳,防止鎖死和永久性的電路損壞,同時(shí)也為了防止開(kāi)機(jī)接通時(shí)的毛刺干擾和降低開(kāi)機(jī)接通的功耗,這些電源輸入必須具有精確的上電序列以及正確

- 關(guān)鍵字: FPGA

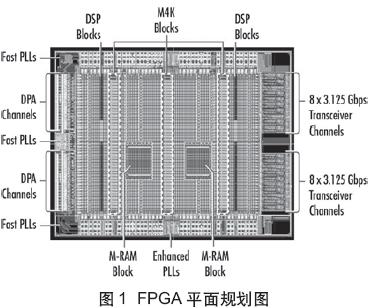

在FPGA中集成高速串行收發(fā)器面臨的挑戰(zhàn)(04-100)

- Altera公司對(duì)PCI Express,串行Rapid I/O和SerialLite等串行標(biāo)準(zhǔn)和協(xié)議的認(rèn)可,將促進(jìn)具有時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR)功能的高速串行收發(fā)器的應(yīng)用。這些曾在4或8位ASSP中使用的收發(fā)器現(xiàn)在可以集成在高端FPGA中。帶有嵌入式收發(fā)器的FPGA占據(jù)更小的電路板空間,具有更高的靈活性和無(wú)需接口處理的兩芯片方案等優(yōu)勢(shì),因此,采用這種FPGA對(duì)電路板設(shè)計(jì)者是很具有吸引力的選擇。 在FPGA中集成收發(fā)器使得接口電路處理工作由電路板設(shè)計(jì)者轉(zhuǎn)向芯片設(shè)計(jì)者。本文闡述在一個(gè)FPGA中集成1

- 關(guān)鍵字: Altera FPGA ASSP ASIC

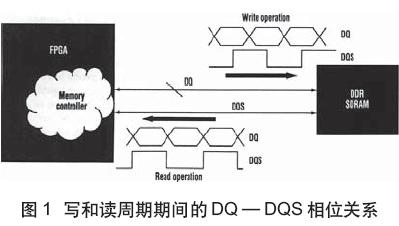

FPGA到高速DRAM的接口設(shè)計(jì)(04-100)

- FPGA做為系統(tǒng)的核心元件正在更多的用于網(wǎng)絡(luò)、通信、存儲(chǔ)和高性能計(jì)算應(yīng)用中,在這些應(yīng)用中都需要復(fù)雜的數(shù)據(jù)處理。 所以,現(xiàn)在FPGA支持高速、外部存儲(chǔ)器接口是必須遵循的。現(xiàn)在的FPGA具有直接接口各種高速存儲(chǔ)器件的專門特性。本文集中描述高速DRAM到FPGA的接口設(shè)計(jì)。 設(shè)計(jì)高速外部存儲(chǔ)器接口不是一件簡(jiǎn)單的任務(wù)。例如,同步DRAM已發(fā)展成高性能、高密度存儲(chǔ)器并正在用于主機(jī)中。最新的DRAM存儲(chǔ)器—DDR SDRAM,DDR2和RLDRAM II支持頻率范圍達(dá)到133MHz(260

- 關(guān)鍵字: Altera FPGA DRAM

基于FPGA的液晶顯示控制器設(shè)計(jì)

- 液晶顯示器由于具有低壓、微功耗、顯示信息量大、體積小等特點(diǎn),在移動(dòng)通信終端、便攜計(jì)算機(jī)、GPS衛(wèi)星定位系統(tǒng)等領(lǐng)域有廣泛用途,成為使用量最大的顯示器件。液晶顯示控制器作為液晶驅(qū)動(dòng)電路的核心部件通常由集成電路組成,通過(guò)為液晶顯示系統(tǒng)提供時(shí)序信號(hào)和顯示數(shù)據(jù)來(lái)實(shí)現(xiàn)液晶顯示。本設(shè)計(jì)是一種基于FPGA(現(xiàn)場(chǎng)可編程門陣列)的液晶顯示控制器。與集成電路控制器相比,F(xiàn)PGA更加靈活,可以針對(duì)小同的液晶顯示模塊更改時(shí)序信號(hào)和顯示數(shù)據(jù)。FPGA的集成度、復(fù)雜度和面積優(yōu)勢(shì)使得其日益成為一種頗具吸引力的高性價(jià)比ASIC替代方案

- 關(guān)鍵字: FPGA 液晶

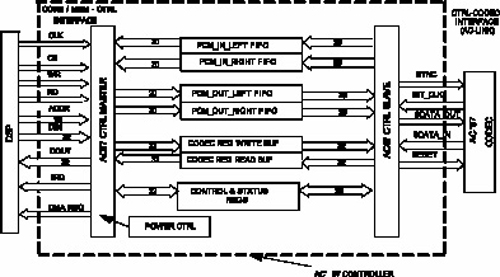

基于SoC的AC'97技術(shù)硬件設(shè)計(jì)

- 引言 符合Audio Codec'97協(xié)議(簡(jiǎn)稱AC'97,是由Intel公司提出的數(shù)字音頻處理協(xié)議)的音頻控制器不但廣泛應(yīng)用于個(gè)人電腦聲卡,并且為個(gè)人信息終端設(shè)備的SOC(如Intel的PXA250)提供音頻解決方案。本文設(shè)計(jì)的音頻控制器可為DSP內(nèi)核提供數(shù)字音頻接口。全文在介紹音頻控制器結(jié)構(gòu)的同時(shí),著重強(qiáng)調(diào)其與內(nèi)核之間數(shù)據(jù)的協(xié)調(diào)傳輸,并給出基于FPGA實(shí)現(xiàn)SoC內(nèi)核仿真環(huán)境對(duì)音頻控制器進(jìn)行功能測(cè)試的方法。 音頻控制器的結(jié)構(gòu)和原理 AC'97系統(tǒng)由音頻編解碼器(Codec)和音頻控

- 關(guān)鍵字: 數(shù)字音頻 接口 DSP FPGA SoC 內(nèi)存

四種常用FPGA/CPLD設(shè)計(jì)思想與技巧之流水線操作

- FPGA/CPLD設(shè)計(jì)思想與技巧之流水線操作本系列討論的四種常用FPGA/CPLD設(shè)計(jì)思想與技巧:乒乓操作、串并轉(zhuǎn)換、流...

- 關(guān)鍵字: CPLD設(shè)計(jì) FPGA 流水線操作 設(shè)計(jì)思想 串并轉(zhuǎn)換 RAKE接收機(jī) 單流 設(shè)計(jì)手段 流水線設(shè)計(jì) 操作時(shí)間

四種常用FPGA/CPLD設(shè)計(jì)思想與技巧之乒乓操作

- FPGA

- 關(guān)鍵字: CPLD設(shè)計(jì) FPGA 乒乓 Xilinx Altera Lattice actel 操作 系統(tǒng)設(shè)計(jì) 思想

FPGA可滿足SMPTE視頻標(biāo)準(zhǔn)對(duì)更高速率的需求

- 主題:FPGA可滿足SMPTE視頻標(biāo)準(zhǔn)對(duì)更高速率的需求SMPTE又制定了通常稱為SMPTE292M的標(biāo)準(zhǔn),支持非壓縮的HDTV視...

- 關(guān)鍵字: SMPTE FPGA 視頻格式 視頻轉(zhuǎn)換 速率 串行傳輸 數(shù)字電影標(biāo)準(zhǔn) HD 模擬音頻 視頻內(nèi)容

FPGA在多制式視頻轉(zhuǎn)換系統(tǒng)中的應(yīng)用

- FPGA

- 關(guān)鍵字: FPGA 視頻轉(zhuǎn)換 多制式 Xilinx Altera Lattice CPLD actel 系統(tǒng)設(shè)計(jì) kinsen

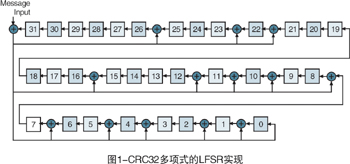

在Virtex-5 FPGA中使用CRC硬模塊

- 數(shù)據(jù)損壞是與數(shù)據(jù)傳輸和存儲(chǔ)有關(guān)的首要問(wèn)題。只要是在通道上傳輸數(shù)據(jù),就總會(huì)有出現(xiàn)某些錯(cuò)誤的有限概率。 關(guān)鍵是接收模塊要能區(qū)分無(wú)錯(cuò)消息和有錯(cuò)消息。檢錯(cuò)有多種方法,其中大多數(shù)都是專門為此目的引入冗余位。數(shù)據(jù)通信中常用的檢錯(cuò)方法包括奇偶碼、漢明碼和循環(huán)冗余校驗(yàn)(CRC),其中CRC使用最廣泛。 CRC根據(jù)一個(gè)給定的數(shù)據(jù)位組算出,然后在傳輸或存儲(chǔ)之前附加到數(shù)據(jù)幀尾部。接收或檢索到幀后,對(duì)其內(nèi)容重新計(jì)算CRC,以此來(lái)驗(yàn)證其有效性,確保數(shù)據(jù)無(wú)誤。 本文簡(jiǎn)述CRC計(jì)算所依據(jù)的原理,并且探討用線性反饋

- 關(guān)鍵字: FPGA

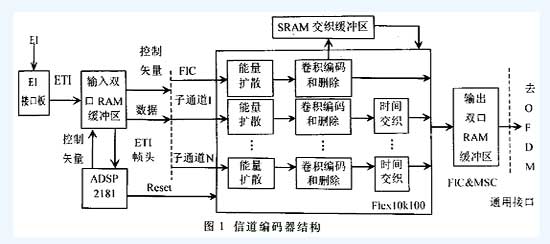

基于FPGA的數(shù)字音頻廣播信道編碼器的實(shí)現(xiàn)

- 摘要:介紹了數(shù)字音頻廣播(DAB)信道編碼的原理和關(guān)鍵技術(shù),并應(yīng)用單片F(xiàn)LEX10K100系列FPGA實(shí)現(xiàn)DAB信道編碼器。 關(guān)鍵詞:數(shù)字音頻廣播(DAB) 信道編碼 FPGA 1 數(shù)字音頻廣播(DAB)發(fā)射系統(tǒng)及信道編碼器 DAB是繼調(diào)幅和調(diào)頻廣播之后的第三代廣播體系。與模擬廣播相比它不僅可以提供高質(zhì)量的聲音信號(hào)(CD音質(zhì)),也可以提供數(shù)據(jù)、圖像等多種其他附加服務(wù)。它可以保護(hù)在高速移動(dòng)接收時(shí)的聲音質(zhì)量,具有很強(qiáng)的抗干擾能力,在同要瓣頻帶寬度和環(huán)境下,DAB可以提供高質(zhì)量的多種多樣的

- 關(guān)鍵字: 數(shù)字音頻 FPGA DAB 編碼器

Xilinx FPGA適應(yīng)不斷變化的廣播視頻潮流

- 電視臺(tái)的演播室需要在不替換龐大的以同軸電纜構(gòu)建的基礎(chǔ)架構(gòu)的情況下,將模擬音頻和視頻轉(zhuǎn)換為數(shù)字音頻和視頻,這樣就逐漸形成了傳輸非壓縮標(biāo)清視頻的串行數(shù)字接口(SDI)協(xié)議。如今,出于重新利用同軸電纜的同樣目的,日益增長(zhǎng)的屏幕分辨率和相關(guān)數(shù)據(jù)速率衍生出了若干新的串行數(shù)據(jù)通信格式。 首先出現(xiàn)的是SDI標(biāo)準(zhǔn),通常稱為SMPTE 259M標(biāo)準(zhǔn),這是由電影與電視工程師協(xié)會(huì)(SMPTE)制定的,于1989年開(kāi)始商業(yè)應(yīng)用。在最初推出之際,用于接口的主要芯片是由ASSP芯片制造商提供的。SDI名義上的數(shù)據(jù)速率是27

- 關(guān)鍵字: Xilinx FPGA

arm+fpga介紹

您好,目前還沒(méi)有人創(chuàng)建詞條arm+fpga!

歡迎您創(chuàng)建該詞條,闡述對(duì)arm+fpga的理解,并與今后在此搜索arm+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)arm+fpga的理解,并與今后在此搜索arm+fpga的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司