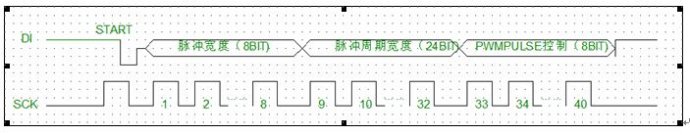

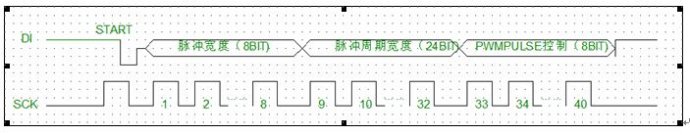

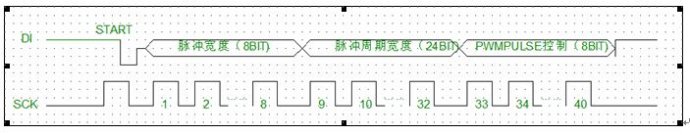

1.線路狀態:在平時不發送數據的時候���,DI 為高電平��。SCK為低電平。2.起始位:SCK 為高的時候,DI 的下降沿決定了一次數據傳送的開始�。也就是說����,在發送數據的時候��,SCK為高電平的期間���,DI 不允許變化��。

本文引用地址:http://www.104case.com/article/201612/330297.htm3.起始位有效后���,SCK的上升沿輸出數據���。

4.時序圖

5.所有數據低位在前

數據為單向發送���,目的是產生寬度可頻率可以調節的信號�。同時產生一路Pwm信號����,本設計只是發送數據部分

代碼:

module SetData(Rst,SCK,DI,Width,Cycle,PWM);

input SCK,DI,Rst;

output reg [7:0]Width;//脈沖寬度

output reg [23:0]Cycle;//周期

output reg [7:0] PWM;//Pwm數據

reg [7:0]Buff;

reg [7:0] Buff1;

reg [2:0]Stage;//狀態變量

reg [5:0]Cnt;

reg Load;

reg INIT;//起始位標記

parameterStatus0= 3b000;//狀態定義

parameterStatus1= 3b001;

parameterStatus2= 3b010;

parameterStatus3= 3b011;

parameterStatus4= 3b100;

parameterStatus5= 3b101;

parameterStatus6= 3b110;

parameterStatus7= 3b111;

always @(negedge Rst,negedge SCK)//產生串并轉換完成信號(8bit)

begin

if(!Rst) Load<=0;

else if ((!SCK)&&(Cnt==8))

Load<=1;

else Load<=0;

end

always @(negedge DI)//檢測起始位

begin

if(SCK==1)INIT<=0;//標記到init 中

else INIT<=1;

end

always @(negedge Rst,posedge SCK,negedge INIT)//狀態轉換

begin

if ((Rst==0) || (INIT==0))//強制到狀態0

begin

Stage<=Status0;

Buff<=0;

end

else if ((SCK==1)&&(Stage==Status0)) begin Stage<=Status1;Cnt<=0; end

else if ((SCK==1)&&(Stage!=Status0))

begin

Buff<={DI,Buff[7:1]};

Cnt <= Cnt+1;

if (Cnt==8)

begin

Cnt<=1;

Stage<=Stage+1;

if (Stage==Status7) Stage<=Status0;

end

end

end

always @(posedge Load,negedge INIT)//組合出需要的數據

begin

if (INIT==0)//如果是起始位,所有數據清零

begin Width <=0;Cycle<=0; PWM<=0; end

else

//begin

case(Stage)//不同狀態下的數據輸出

//Status0:

Status1: Width<=Buff;//脈寬數據

Status2: Cycle<={ Cycle[23:8],Buff};//周期數據

Status3: Cycle<={ Cycle[23:16],Buff,Cycle[7:0]};

Status4: Cycle<={ Buff,Cycle[15:8],Cycle[7:0]};

Status5: PWM<=Buff;//PWM數據

endcase

// end

end

endmodule

仿真結果

注意圖中認為中斷了數據發送(通過設置起始位來實現)。

初學verilog語言���,用的可能不夠規范,主要是不習慣不能在不同進程里對同一個變量賦值的約束����,只好加一個init變量進行信號傳遞����。

評論