基于FPGA技術的RS232接口時序電路設計

1 發送邏輯電路的設計

本文引用地址:http://www.104case.com/article/201612/328662.htm1.1 時序近似

RS 232接口可選的波特率如9 600b/s,115.2 Kb/s等同11.059 2 MHz的時鐘有著整數倍的關系,但通常情況下提供FPGA的時鐘大多采用頻率為40~80 MHz,同11.059 2 MHz之間存在一定的時序誤差。

例如一個由1個起始位,8個數據位,1個停止位組成,假定串行信號的波特率為9 600b/s,則每個位的時序時間為:

104 166.666 666 666 666 666 666 666 666 67 ns

相當于80 MHz計數器計數到:

8 333.333 333 333 333 333 333 333 333 333 3舍去小數部分。

由80 MHz驅動的計數器產生時序時每個字符誤差為4.166 666 666 666 666 666 666 666 666 666 7 ns。這樣由10個字符組成的一次發射時序誤差約為41.7 ns小于1/1 000可以忽略不計。

1.2 發送時序設計

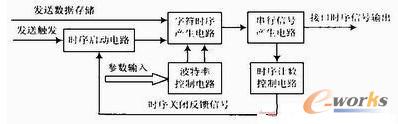

RS 232接口的時序電路由啟動電路、字符產牛電路、同步時鐘產生電路。波特率控制電路,和時序關閉電路組成。發送時序電路原理框圖如圖1所示。

圖1 發送時序電路原理框圖

1.3 發送電路原理描述

以波特率為9 600b/s的時序為例,在發送數據之前,系統微處理器將相應波特率參數鎖存在FPGA內部的波特率控制電路的寄存器內(由觸發器構建),使每次輸出的字符同步信號的周期為104.167μs(對應波特率9 600b/s)。

當系統發出發送啟動信號時,字符時序電路以每個字符104.167μs的速率在預發射數據的邏輯電平控制之下輸出時序信號,同時在時序中插入停止位和起始位字符信號。

在完成上述發送時序的過程中,時序計數控制電路會檢測發送時序的工作狀態,當檢測每次時序的停止位完成輸出后,時序計數控制電路會發出時序關閉反饋信號,使電路回復到預發射的初始工作狀態,并等待處理器再次觸發時序電路和對數據參數的重置。

2 接收邏輯電路的設計

2.1 接收時序設計

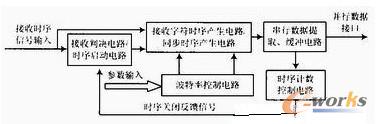

接收時序電路原理框圖如圖2所示。

圖2 接收時序電路原理框圖

2.2 接收電路原理描述

以波特率為9 600b/s的時序為例,在接收數據之前系統微處理器將相應波特率參數鎖存在FPGA內部的波特率控制電路的寄存器內(由觸發器構建),使每次輸出的字符位同步信號的周期為104.167 μs(對應波特率9 600b/s)。字符位同步信號是接收電路存儲接收數據邏輯狀態的關鍵。作為同步時鐘信號,該信號可驅動接收到的串行數據電平輸入移位寄存器內并鎖存。

當系統接收到一幀串行信號時,首先要判斷是否是新的一幀數據,接收判決電路通過對輸入串行信號的起始位字符脈寬進行裁決,按照RS 232接口通信協議在某一特性波特率下,一幀信號的起始是一定脈寬的負脈沖。通過計數器可以檢測到負脈沖的起始時間和脈沖寬度,當脈沖寬度達到某一數值時啟動接收時序。

接收時序電路會通過被記錄下的接收信號的準確到達時間,推算出每個串行數據位對應的時序時刻,從而輸出對應每個位中間時刻的字符位同步信號(脈沖)作為接收移位寄存器的同步時鐘信號驅動移位寄存器對接收數據電平的記錄。

被鎖存的數據通過并行總線被系統微處理器提取。這一過程可以通過對處理器的中斷實現,但需要接收時序電路在完成數據接收后立即產生一個中斷信號,通知處理器提取接收數據。

接收時序計數器會對接收時序時間進行檢測,當接收時序到達結束時刻時,其輸出的時序關閉反饋信號會使接收電路恢復到初始工作電路,等待下一幀數據的到達。

3 結論

通過FPGA實現RS 232接口時序邏輯電路,已經在工程實踐過程中實現了接口標準規定的全部功能。可以認為,通過FPGA的邏輯電路設計可以完全取代專用芯片。介于FPGA的可塑性和靈活性,可以通過相應邏輯電路設計實現包括以太網,USB、RS 485等常見的數據接口。

評論