S3C6410 時鐘初始化

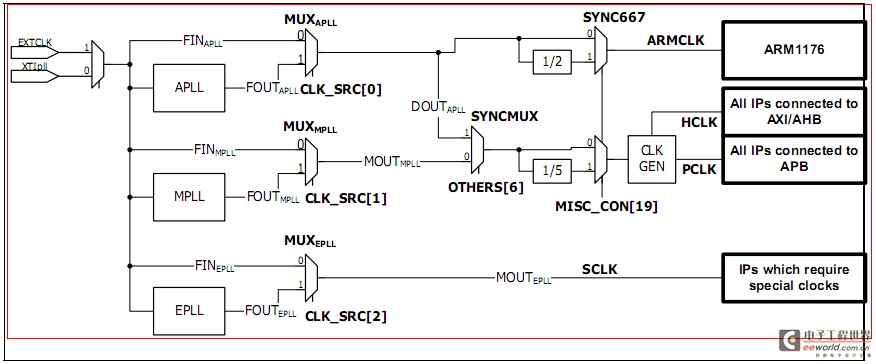

S3C6410里包含三個PLL(鎖相環),APLL, MPLL, EPLL,通過設置它們將輸入時鐘同步輸出達到操作CPU的工作頻率的目的。如圖1-1所示。

Voltage Controlled Oscillator (VCO)P[5:0]位來設置FIN進行分頻。通過設置Main-Divider分頻數,分頻壓控振蕩器產生的輸出時鐘頻率,分頻之后的低頻進入鑒相器ScalerS[2:0]位設置PLL的輸出時鐘頻率都可以通過

PLL的時鐘選擇和輸入參照時鐘

圖1-2描述了時鐘產生邏輯。S3C6410有三個PLL鎖相環,工作時鐘也分為三組,APLL用來為ARM芯片提供工作時鐘,MPLL為AXI,AHB,APB總線上設備提供工作時鐘,EPLL為特殊外設,如:視頻解碼器,圖片編碼器等,提供工作時鐘。

圖1-2時鐘產生邏輯單元

CLK_SRC寄存器的低三位CLK_SRC[2:0]分別控制三種工作時鐘。當對應位被置位,則產生對應PLL的工作時鐘。否則,不會產生對應的PLL工作時鐘。

3.三種工作時鐘的產生

ARM1176最高產生667Mhz的工作頻率。用戶可以通過設置內部時鐘分頻器的值來控制輸出工作時鐘,而不用修改PLL的工作頻率。分頻器可以選擇1~16的分頻數。ARM內核可以通過修改分頻器的值來減少系統電源的損耗。

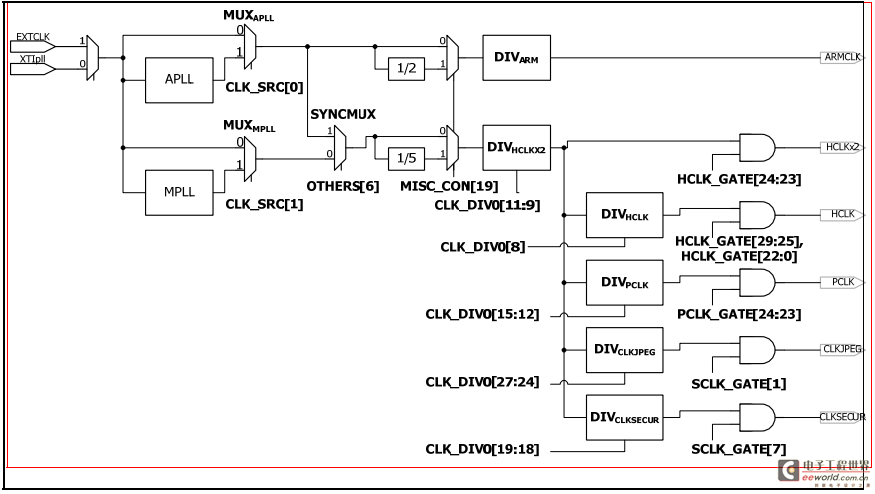

S3C6410內部含有AXI,AHB和APB總線,通過不同的總線控制不同的外設,關閉總線上的時鐘頻率可以達到系統節能的目的。AXI,AHB總線最高工作在133MHz頻率下,APB總線最高工作在66MHz頻率下。由于APB和AXI,AHB總線上二者工作頻率不一致,在這兩種總線上進行數據同步傳輸時會采用特殊邏輯單元,如圖1-3所示。

圖1-3系統總線工作頻率設置

HCLKX2時鐘由DDR0,DDR1兩個DDR控制器產生,其最高可以以266MHz頻率發送和接收數據。每個HCLKX2時鐘可以根據用戶需要分別被關閉掉來減少系統損耗。AHB總線上的時鐘由DIV(HCLK)分頻器分頻后輸出,同樣AHB總線上的外設也可以被關閉掉以節省電源消耗。HCLK_GATE寄存器用來關閉工作在HCLKX2和HCLK時鐘上的外設。

慢速設備連接在APB總線上。APB時鐘最高工作在66MHz,通過DIV(PCLk)分頻器來進行分頻設置,通過設置PCLK_GATE寄存器來關閉對應的APB總線上的外設。根據S3C6410硬件手冊說明,AHB總線和APB總線上的頻率必須是偶數,例如,如果DIV(HCLK)對應控制位CLK_DIV[8]設置為1,則DIV(PCLK)對應位CLK_DIV0[15:12]必須設置為1,3,5,…等奇數。否則,APB總線上的外設不能正解的進行數據傳輸。

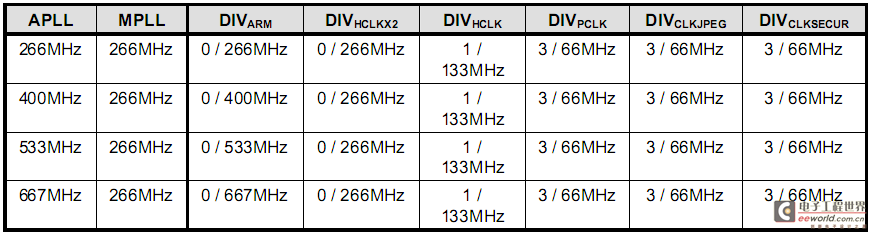

AHB總線上的JPEG和安全相關子系統不能工作在133MHz,AHB總線專門為這樣低頻子系統提供低頻工作時鐘,通過設置DIV(CLKJPEG)和DIV(CLKSECUR)分頻位來設置其工作頻率。因此,同樣在APB總線上也有類似的這種限制設定,DIV(CLKJPEG)和DIV(CLKSECUR)對應的CLK_DIV0[27:24]分頻位和CLK_DIV0[19:18]分頻位必須是奇數,二者的和是偶數。如表1-1所示,官方給出了推薦的設置參數。

表1-1官方推薦參數

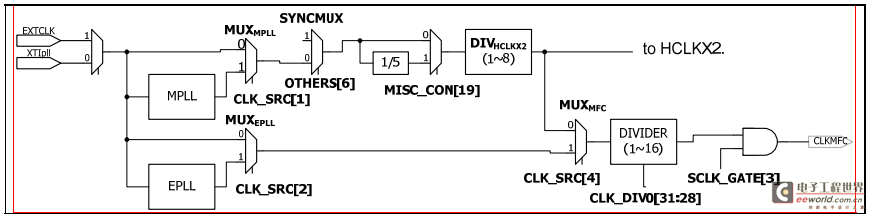

4.MFC模塊時鐘的產生

MFC模塊需要特殊的時鐘,如圖1-5所示。

圖1-5 MFC時鐘產生邏輯

MFC時鐘源可以從HCLKX2和MOUT(EPLL)中選擇。MFC的工作時鐘使用HCLKX2來分頻。默認HCLKX2時鐘頻率為266MHz。因此,CLK_DIV0[31:28]必須設置為b0001來產生MFC工作的133MH時鐘。當MFC模塊不需要工作在高性能模式下時,有兩種方式可以減少MFC模塊工作頻率來達到減少MFC模塊的功耗。第一種方式是設置CLK_SRC[4]使用EPLL的輸出時鐘,另外一種方式是設置CLK_DIV0[31:28]的分頻數,同時,設置CLK_SRC[4]位,這樣低頻工作時鐘就可以提供給MFC模塊。EPLL輸出時鐘是與HCLKX2和HCLK獨立的。

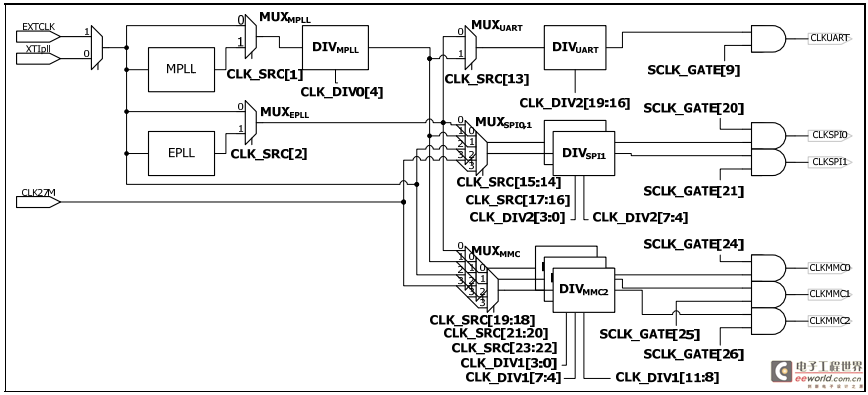

5.UART,SPI,MMC工作時鐘的產生

如圖1-6所示,是上述三種外設工作時鐘邏輯。

圖1-6 UART,SPI,MMC工作時鐘邏輯模塊

通過設置CLK_DIV2[19:16]位來設置UART的工作頻率的分頻數,通過SCLK_GATE[9]來開啟關閉UART時鐘源。

該模塊中有一個額外的時鐘源CLK27M,使用該時鐘源可以提供更多的可選工作時鐘。

6.時鐘的開啟/關閉控制

HCLK_GATE,PCLK_GATE和SCLK_GATE用來控制三種時鐘源的產生,如果對應的位被設置,對應時鐘就會產生。

HCLK_GATE控制HCLK總線上的外設工作時鐘的產生,PCLK_GATE控制PCLK總線上的外設工作時鐘的產生,PCLK總線上的外設需要特定的時鐘,它們通過SCLK_GATE來設置。

7.同步667MH操作模式

根據S3C6410硬件手冊,ARMCLK和HCLK的時鐘比必須是整數,用來同步ARM內核和AXI總線接口二者的時鐘。S3C6410沒有對CPU工作在533MHz做限制,ARMCLK = 533MHz,HCLKX2=266MHz,HCLK=133MH,不過,對于工作在533MHz以上時,例如667Mhz時,只能支持1:2.5:5的時鐘比(ARMCLK = 667MHz,HCLKX2=266MHz,HCLK=133MH)

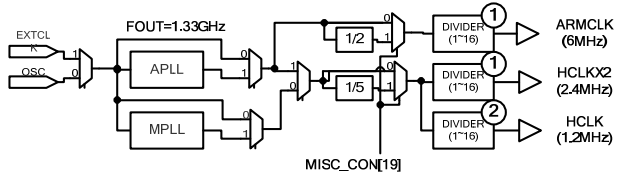

8.時鐘分頻

圖1-7時鐘分頻模塊

如圖1-7所示,時鐘分頻模塊產生三種時鐘,ARMCLK,HCLKX2,HCLK。時鐘分頻器包含兩部分,預分頻器組和后分頻器組,預分頻器包含一個1/2預分頻器和1/5預分頻器,這兩個分頻器是固定的不能被軟件配置,而后分頻器可以通過配置CLK_DIV0寄存器方式進行配置。當MISC_CON的SYNC667MHz位被設置時,兩個預分頻器同時工作,產生APLL的分頻經過預分頻器分頻的時鐘,如果APLL的FOUT輸出頻率為1.33GHz,預分頻器ARMCLK的輸出為667Mhz,預分頻器HCLK的輸出為266MHz。這樣經過分頻的時鐘可以通過CLK_DIV0寄存器進行配置。

我們打算將ARM內核時鐘設置為官方推薦的穩定的533MHz,讓APLL為AHB,APB輸出工作頻率。讓MPLL為UART等外設提供工作頻率,EPLL不工作。同時設置HCLKX2為266MHz,HCLK為133MHz,PCLK為66.5MHz,UART工作時鐘為66.5MHz。

1.選擇HCLKX2, HCLK, PCLK的時鐘源,由圖1-2可知其時鐘源可以通過OTHER[6]選擇是由DOUT_APLL還是MOUT_MPLL,我們選擇從DOUT_APLL。

ldrr0, =CLOCK_BASE;0x7e00f000

ldrr1, [r0, #OTHERS_OFFSET];選擇MPLL的時鐘源

movr2, #0x40

orrr1, r1, r2

strr1, [r0, #OTHERS_OFFSET]

nop

nop

nop

nop

;選擇CPU的同步工作模式

ldrr2, =0x80

orrr1, r1, r2

strr1, [r0, #OTHERS_OFFSET]

;測試是否已經工作在同步模式下

check_syncack

ldrr1, [r0, #OTHERS_OFFSET]

ldrr2, =0xf00

andr1, r1, r2

cmpr1, #0xf00

bnecheck_syncack

ldrr1, [r0, #OTHERS_OFFSET];選擇MPLL的時鐘源

movr2, #0x40

orrr1, r1, r2

strr1, [r0, #OTHERS_OFFSET]

nop

nop

nop

nop

;選擇CPU的同步工作模式

ldrr2, =0x80

orrr1, r1, r2

strr1, [r0, #OTHERS_OFFSET]

;測試是否已經工作在同步模式下

check_syncack

ldrr1, [r0, #OTHERS_OFFSET]

ldrr2, =0xf00

andr1, r1, r2

cmpr1, #0xf00

bnecheck_syncack

2.設置變頻鎖定時間,當系統時鐘修改之后要經過段LOCK時間

;設置變頻鎖定時間

movr1, #0xff00

orrr1, r1, #0xff

strr1, [r0, #APLL_LOCK_OFFSET]

strr1, [r0, #MPLL_LOCK_OFFSET]

strr1, [r0, #EPLL_LOCK_OFFSET]

movr1, #0xff00

orrr1, r1, #0xff

strr1, [r0, #APLL_LOCK_OFFSET]

strr1, [r0, #MPLL_LOCK_OFFSET]

strr1, [r0, #EPLL_LOCK_OFFSET]

3.設置ARMCLK, HCLKX2, HCLK, PCLK的分頻

各種頻率的關系如圖1-3所述:

APLL或MPLL產生的輸出頻率經過OTHER[6]選擇之后再經過MISC_CON[19]選擇是否被1/5分頻,產生的輸出頻率進入DIV_HCLKx2,根據CLK_DIV0的不同位設置HCLKX2,HCLK,PCLK,CLKJPEG,CLKSECUR的輸出頻率。其值設置情況如CLK_DIV0寄存器描述內容所述。

l我們將MPLL選擇DOUT_APLL,MISC_ON[19]不進行分頻,DOUT_APLL產生的時鐘(533MHz)直接進入到DIV_HCLKX2分頻器中。

l根據硬件手冊可知,HCLKX2的頻率固定為266MHz,所以HCLKX2_RATIO設置為0b1

lHCLK上掛接有內存,Mobile DDR內存最高工作在133MHz,所以HCLK最高主頻設置為HCLKX2的1/2,即:HCLK_RATIO = 0b1

l設置PCLK上的工作頻率為66.5MHz,即:PCLK_RATIO = 0b11

l設置ARM內核工作頻率為553MHz,即:ARM_RATIO = 0b0

l設置DOUT_MPLL為266MHz,為后面UART提供時鐘源,即:MPLL_RATIO = 0b0

l其它時鐘頻率保持默認值

; MPLL_RATIO = 0<<4, ARM_RATIO = 0

; DOUT_MPLL = MOUT_MPLL/(MPLL_RATIO + 1)

;即ARMCLK = DOUT_APLL / (ARM_RATIO + 1)

;即ARMCLK = 533MHz, DOUT_MPLL = 266MHz

; HCLKX2_RATIO = 1<<9 , HCLK_RATIO = 1<<8,PCLK_RATIO = 3<<12, HCLKX2IN = 533

;即HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) = 266

;即HCLK = HCLKX2 / (HCLK_RATIO + 1) = 133

;即PCLK = HCLKX2 / (PCLK_RATIO + 1) = 66.5

ldrr1, [r0, #CLK_DIV0_OFFSET]

bicr1, r1, #0xff00

bicr1, r1, #0xff

ldrr2, =0x3300

orrr1, r1, r2

strr1, [r0, #CLK_DIV0_OFFSET]

; DOUT_MPLL = MOUT_MPLL/(MPLL_RATIO + 1)

;即ARMCLK = DOUT_APLL / (ARM_RATIO + 1)

;即ARMCLK = 533MHz, DOUT_MPLL = 266MHz

; HCLKX2_RATIO = 1<<9 , HCLK_RATIO = 1<<8,PCLK_RATIO = 3<<12, HCLKX2IN = 533

;即HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) = 266

;即HCLK = HCLKX2 / (HCLK_RATIO + 1) = 133

;即PCLK = HCLKX2 / (PCLK_RATIO + 1) = 66.5

ldrr1, [r0, #CLK_DIV0_OFFSET]

bicr1, r1, #0xff00

bicr1, r1, #0xff

ldrr2, =0x3300

orrr1, r1, r2

strr1, [r0, #CLK_DIV0_OFFSET]

4.設置UART工作時鐘

由圖1-6可知,通過設置CLK_SRC[1]選擇DOUT_MPLL的工作時鐘是否進行倍頻,通過設置CLK_DIV0[4]對時鐘進行分頻,再通過CLK_SRC[13]選擇UART的工作時鐘源,設置CLK_DIV2[19:16]位用于分頻UART工作時鐘。由前面可知DOUT_MPLL = 266MHz,UART選擇其作為自己工作時鐘源,則對其進行1/4分頻可以得到66.5MHz。

如下表可知:設置寄存器CLK_DIV2[19:16] = 0b11,同時還要設置CLK_SRC[13] = 0b1即可。

;設置UART串口的分頻數寄存器CLK_DIV2

ldrr1, [r0, #CLK_DIV2_OFFSET]

bicr1, r1, #0x70000

orrr1, r1, #0x30000;設置其值為3,即CLKUART = CLKUARTIN / 4

strr1, [r0, #CLK_DIV2_OFFSET]

ldrr1, [r0, #CLK_DIV2_OFFSET]

bicr1, r1, #0x70000

orrr1, r1, #0x30000;設置其值為3,即CLKUART = CLKUARTIN / 4

strr1, [r0, #CLK_DIV2_OFFSET]

5.使能APLL,EPLL鎖相環

根據硬件手冊上的說明設置APLL, EPLL的M,D,S分頻數。

APLL產生533MHz的FOUT_APLL

EPLL產生266MHz的MOUT_EPLL

;使能APLL鎖相環,配置M,D,S分頻數, according to Datasheet FOUT_APLL = 533 then

; APLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 1

ldrr1, = 0x810a0301

strr1, [r0, #APLL_CON_OFFSET]

;使能MPLL鎖相環,配置M,D,S分頻數

; MPLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 2

ldrr1, = 0x810a0302

strr1, [r0, #MPLL_CON_OFFSET]

; APLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 1

ldrr1, = 0x810a0301

strr1, [r0, #APLL_CON_OFFSET]

;使能MPLL鎖相環,配置M,D,S分頻數

; MPLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 2

ldrr1, = 0x810a0302

strr1, [r0, #MPLL_CON_OFFSET]

6.設置對應時鐘源寄存器,為各種外設提供時鐘頻率

; UART_SEL = 0b1

; MPLL_SEL = 0b1, APLL_SEL = 0b1

ldrr1, [r0, #CLK_SRC_OFFSET]

ldrr2, =0x2005;同時設置UART的時鐘源來自MPLL

orrr1, r1, r2

strr1, [r0, #CLK_SRC_OFFSET]

; MPLL_SEL = 0b1, APLL_SEL = 0b1

ldrr1, [r0, #CLK_SRC_OFFSET]

ldrr2, =0x2005;同時設置UART的時鐘源來自MPLL

orrr1, r1, r2

strr1, [r0, #CLK_SRC_OFFSET]

評論