ARM處理器模式及寄存器

- ARM微處理器支持7種運行模式,分別為:

用戶模式(usr): ARM處理器正常的程序執行狀態。快速中斷模式(fiq):用于高速數據傳輸或通道處理。外部中斷模式(irq):用于通用的中斷處理。管理模式(svc): 操作系統使用的保護模式。軟中斷和復位數據訪問中止模式(abt): 當數據或指令預取終止時進入該模式,可用于虛擬存儲及存儲保護。系統模式(sys): 運行具有特權的操作系統任務。未定義指令中止模式(und):當未定義的指令執行時進入該模式,可用于支持硬件協處理器的軟件仿真

- 除用戶模式外的其余6種模式都稱為特權模式,這些模式下,程序可以訪問所有的系統資源,也可以任一進行處理器模式切換。其中,除系統模式外,其他5種模式又稱為異常模式

二、ARM寄存器

(一)ARM工作狀態下的寄存器組織

ARM處理器共有37個寄存器。其中包括:

- 31個通用寄存器,包括程序計數器(PC)在內。這些寄存器都是32位寄存器

- 6個32位狀態寄存器。

表1各種處理器模式下的寄存器

用戶模式 | 系統模式 | 特權模式 | 中止模式 | 未定義指令模式 | 外部中斷模式 | 快速中斷模式 |

R0 | R0 | R0 | R0 | R0 | R0 | R0 |

R1 | R1 | R1 | R1 | R1 | R1 | R1 |

R2 | R2 | R2 | R2 | R2 | R2 | R2 |

R3 | R3 | R3 | R3 | R3 | R3 | R3 |

R4 | R4 | R4 | R4 | R4 | R4 | R4 |

R5 | R5 | R5 | R5 | R5 | R5 | R5 |

R6 | R6 | R6 | R6 | R6 | R6 | R6 |

R8 | R8 | R8 | R8 | R8 | R8 | R8_fiq |

R9 | R9 | R9 | R9 | R9 | R9 | R9_fiq |

R10 | R10 | R10 | R10 | R10 | R10 | R10_fiq |

R11 | R11 | R11 | R11 | R11 | R11 | R11_fiq |

R12 | R12 | R12 | R12 | R12 | R12 | R12_fiq |

R13 | R13 | R13_svc | R13_abt | R13_und | R13_inq | R13_fiq |

R14 | R14 | R14_svc | R14_abt | R14_und | R14_inq | R14_fiq |

PC | PC | PC | PC | PC | PC | PC |

CPSR | CPSR | CPSR SPSR_svc | CPSR SPSR_abt | CPSR SPSR_und | CPSR SPSR_inq | CPSR SPSR_fiq |

- 當發生異常中斷時,處理器進入相應的異常模式。在每一種異常模式下都有相應的一組寄存器,供相應的異常處理程序使用,這樣就可以保證在進入異常模式時,用戶模式下的寄存器(保存了程序運行狀態)不被破壞。

- 系統模式不是通過異常進入的,他和用戶模式具有完全一樣的寄存器

1、通用寄存器

通用寄存器通常分為以下三類:

未備份寄存器:R0——R7

備份寄存器:R8——R14

程序計數器PC,即R15

未備份寄存器R0——R7:

R0~R7。在所有的處理器模式下指的都是同一個物理寄存器。在異常中斷造成處理器模式切換時,由于不同的處理器模式使用相同的物理寄存器,可能造成寄存器中數據被破壞。

備份寄存器R8~R14:

(1)寄存器R8~R12

每個寄存器對應兩個不同的物理寄存器。例如,當使用快速中斷模式下的寄存器時,寄存器R8和寄存器R9分別記作R8_fiq、R9_fiq;當使用用戶模式下的寄存器時,寄存器R8和寄存器R9分別記作R8_usr、R9_usr等。在這兩種情況下使用的是不同的物理寄存器。系統沒有將這幾個寄存器用于任何的特殊用途,但是當中斷處理非常簡單,僅僅使用R8~R14寄存器時,FIQ處理程序可以不必執行保存和恢復中斷現場的指令,從而可以使中斷處理過程非常迅速。對于備份寄存器R13和R14來說,每個寄存器對應6個不同的物理寄存器,其中的一個是用戶模式和系統模式共用的;另外的5個對應于其他5種處理器模式。

(2)寄存器R13在ARM中常用作棧指針(Stack Point,SP)

- 在ARM指令集中,這只是一種習慣的用法,并沒有任何指令強制性的使用R13作為棧指針,用戶也可以使用其他的寄存器作為棧指針;而在Thumb指令集中,有一些指令強制性地使用R13作為棧指針。

- 每一種異常模式擁有自己的物理的R13。應用程序初始化該R13,使其指向該異常模式專用的棧地址。當進入異常模式時,可以將需要使用的寄存器保存在R13所指的棧中;當退出異常處理程序時,將保存在R13所指的棧中的寄存器值彈出。這樣就使異常處理程序不會破壞被其中斷程序的運行現場。

(3)寄存器R14又被稱為連接寄存器(Link Register,LR)

- 在ARM體系中具有下面兩種特殊的作用:每一種處理器模式自己的物理R14中存放在當前子程序的返回地址。當通過BL或BLX指令調用子程序時,R14被設置成該子程序的返回地址。在子程序中,當把R14的值到程序計數器PC中時,子程序即返回。

- 當異常中斷發生時,該異常模式特定的物理R14被設置成該異常模式將要返回的地址,對于有些異常模式,R14的值可能與將返回的地址有一個常數的偏移量。具體的返回方式與上面的子程序返回方式基本相同。

- R14寄存器也可以作為通用寄存器使用。

程序計數器R15(PC)

- 程序計數器R15又被記作PC。它雖然可以作為一般的通用寄存器使用,但是有一些指令在使用R15時有一些特殊限制。當違反了這些限制時,該指令執行的結果將是不可預料的。

- 由于ARM采用了流水線機制,當正確讀取了PC的值時,該值為當前指令地址值加8個字節。也就是說,對于ARM指令集來說,PC指向當前指令的下兩條指令的地址。(因為ARM使用RISC精簡指令集,ARM的一條指令所占內存為32位,4個字節。所以當一條指令正確讀取時,該寄存器指向當前指令地址加8,即指向下兩條指令的地址)

- 當成功地向R15中寫入一個地址數值時,程序將跳到該地址執行。由于ARM指令是字對齊的,所以PC值的第0位和第1位總為0。需要注意的是,當使用指令STR/STM保存R15時,保存的可能是當前指令地址值加8字節,也可能保存的是當前指令地址加12字節。到底是哪種方式,取決于芯片具體設計方式。無論如何,在同一芯片中,要么采用當前指令地址加8,要么采用當前指令地址加12,不能有些指令采用當前指令地址加8,另一些指令采用當前指令地址加12。因此對于用戶來說,盡量避免使用STR/STM指令來保存R15的值。當不可避免這種使用方式時,可以先通過一些代碼來確定所用的芯片使用的是哪種實現方式。

- 對于ARM版本4以及更高的版本,程序必須保證寫入R15寄存器的地址值的bits[1:0]為0b00;否則將會產生不可預知的結果。

- 對于Thumb指令集來說,指令是半字對齊的。處理器將忽略bit[0],即寫入R15的地址值首先與0XFFFFFFFE做與操作,再寫入R15中。

- 還有—些指令對于R15的用法有一些特殊的要求。比如,指令BX利用bit[0]來確定是ARM指令,還是Thumb指令。這種讀取PC值和寫入PC值的不對稱的操作需要特別注意。

注:PC指向的地址是取指單元要取指令的地址,而不是當前執行的指令。

2、程序狀態寄存器

CPSR(當前程序狀態寄存器)可以在任何處理器模式下被訪問。它包含了條件標志位、中斷禁止位、當前處理器模式標志以及其他的一些控制和狀態位。每一種處理器模式下都有一個專用的物理狀態寄存器,稱為SPSR(備份程序狀態寄存器)。當特定的異常中斷發生時,這個寄存器用于存放當前程序狀態寄存器(CPSR)的內容。在異常中斷程序退出時,可以用SPSR中保存的值來恢復CPSR。

由于用戶模式和系統模式不是異常中斷模式,所以它們沒有SPSR。當在用戶模式或系統模式中訪問SPSR,將會產生不可預知的結果。

CPSR的格式如下所示。SPSR格式與CPSR格式相同。

31 | 30 | 29 | 28 | 27 | 26 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

N | Z | C | V | Q | DNM(RAZ) | I | F | T | M4 | M3 | M2 | M1 | M0 |

1.條件標志位

N(Negative)、Z(Zero)、C(Carry)及V(oVerflow)統稱為條件標志位。大部分的ARM指令可以根據CPSR中的這些條件標志位來選擇性地執行。

在ARM狀態下,絕大多數的指令都是有條件執行的。

在Thumb狀態下,僅有分支指令是有條件執行的。

N Negative 對于有符號運算,如果結果是負數則置位Z Zero 如果結果是零則置位C Carry 對于無符號運算,如果發生進位則置位V Overflow 對于有符號運算,如果發生溢出則置位I IRQ 中斷禁用F FIQ 快速中斷禁用

標志位 | 含義 |

N | 本位設置成當前指令運算結果的bit[31]的值 當兩個補碼表示的有符號整數運算時,N=1表示運算的結果為負數;N=0表示結果為正數或零 |

Z | Z=1表示運算的結果為零;Z=0表示運算的結果不為零。 對于CMP指令,Z=1表示進行比較的兩個數大小相等。 |

| C | 下面分4種情況討論C的設置方法: 在加法指令中(包括比較指令CMN),當結果產生了進位,則C=1,表示無符號數運算發生上溢出;其他情況下C=0。 在減法指令中(包括比較指令CMP),當運算中發生借位則C=0表示無符號數運算發生下溢出;其他情況下C=1。 對于包含移位操作的非加/減法運算指令,C中包含最后一次溢出的位數數值。 對于其他非加/減法運算指令,C位的值通常不受影響。 |

V | 對于加/減法運算指令,當操作數和運算結果為二進制的補碼表示的帶符號數時V=1表示符號位溢出。 通常其他的指令不影響V位,具體可參考各指令的說明。 |

2.Q標志位

在ARMv5的E系列處理器中,CPSR的bit[27]稱為Q標志位,主要用于指示增強的DSP指令是否發生了溢出。同樣的SPSR中的bit[27]也稱為Q標志位,用于在異常中斷發生時保存和恢復CPSR中的Q標志位。

在ARM v5以前的版本及ARM v5的非E系列的處理器中,Q標志位沒有被定義。CPSR的bit[27]屬于DNM(RAZ)。

3.CPSR中的控制位

CPSR的低8位I、F、T及M[4:0]統稱為控制位。當異常中斷發生時這些位發生變化。在特權級的處理器模式下,軟件可以修改這些控制位。

1)中斷禁止位

- 當I=1時禁止IRQ中斷。

- 當F=1時禁止FIQ中斷。

2)T控制位

T控制位用于控制指令執行的狀態,即說明本指令是ARM指令,還是Thumb指令。對與不同版本的ARM處理器,T控制位的含義不同。

對于ARMv4以及更高版本的T系列的ARM處理器,

- T=0表示執行ARM指令。

- T=1表示執行Thumb指令。

對于ARMv5以及更高的版本的非T系列的ARM處理器,T控制位含義如下:

- T=0表示執行ARM指令。

- T=1表示強制下一條執行的指令產生未定義指令中斷。

3)M控制位

控制位M[4:0]控制處理器模式,具體含義如表3所示。

表3控制位M[4:0]的含義

M[4:0] | 處理器模式 | 可訪問的寄存器 |

0b10000 | User | PC,R14一R0,CPSR |

0b10001 | FIQ | PC,R14_fiq-R8_flq,R7~R0,CPSR,SPSR_nq |

0b10010 | 1RQ | PC,R14 _irq-R13 _irq,R12一R0,CPSR,SPSR_ irq |

0b10011 | Supervisor | PC,R14_ svc-R13 _svc,R12~R0,CPSR,SPSR_svc |

0b10111 | Abort | PC,R14_abt-R13_abt,R12~R0,CPSR,SPSR_abt |

0b11011 | Undefined | PC,R14_und-R13_und,R12~R0,CPSR,SPSR_ und |

4.CPSR中的其他位

CPSR中的其他位用于將來ARM版本的擴展。應用軟件不要操作這些位,以免與ARM將來版本的擴展沖突。

(二)Thumb工作狀態下的寄存器組織

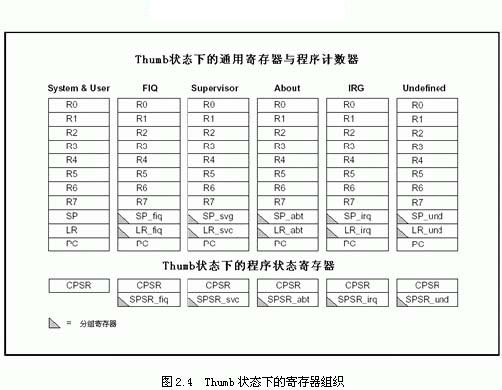

Thumb狀態下的寄存器集是ARM狀態下寄存器集的一個子集,程序可以直接訪問8個通用寄存器(R7~R0)、程序計數器(PC)、堆棧指針(SP)、 連接寄存器(LR)和CPSR。同時,在每一種特權模式下都有一組SP、LR和SPSR。圖2.4表明Thumb狀態下的寄存器組織。

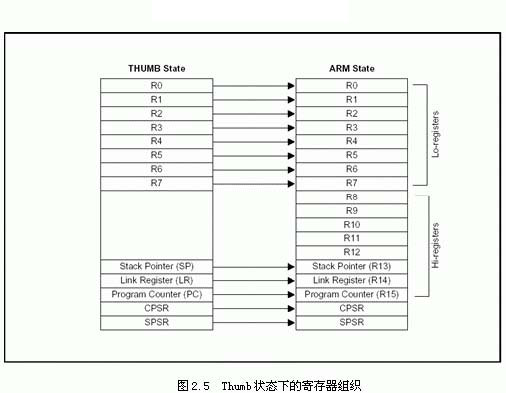

Thumb狀態下的寄存器組織與ARM狀態下的寄存器組織的關系:

─ Thumb狀態下和ARM狀態下的R0~R7是相同的。

─ Thumb狀態下和ARM狀態下的CPSR和所有的SPSR是相同的。

─ Thumb狀態下的SP對應于ARM狀態下的R13。

─ Thumb狀態下的LR對應于ARM狀態下的R14。

─ Thumb狀態下的程序計數器對應于ARM狀態下R15

以上的對應關系如圖2.5所示:

訪問THUMB狀態下的高位寄存器(Hi-registers):

在Thumb狀態下,高位寄存器R8~R15并不是標準寄存器集的一部分,但可使用匯編語言程序受限制的訪問這些寄存器,將其用作快速的暫存器。使用帶特殊變量的MOV指令,數據可以在低位寄存器和高位寄存器之間進行傳送;高位寄存器的值可以使用CMP和ADD指令進行比較或加上低位寄存器中的值。

評論